大多数集成电路 (IC) 设计人员采用先进的工艺技术节点,以利用持续尺寸缩减所实现的性能、密度和功能提升,以及延迟减少和功耗下降等优势。转用鳍式场效应晶体管 (FinFET)、全耗尽型绝缘硅 (FDSOI) 和环绕栅极 (GAA) 晶体管等新器件架构,可以扩大栅极长度缩减范围,但也会导致相邻几何形状之间的寄生交互增加。三维集成电路 (3D-IC) 设计越来越受到关注,因为它有望在提供器件缩减的同时进一步降低成本 ,但它需要验证元器件之间的寄生效应和多种工艺上的互连。

Calibre® xACT™ 解决方案为互连建模提供了新的寄生参数提取 (PEX) 选项,可确保准确捕获非平面器件的寄生和版图相关效应,以及为新兴 3D-IC 设计提供精确的提取和建模。这些选项还能为下游分析提供网表输入。通过在验证流程中实施这些先进的 PEX 解决方案,设计人员可以成功实现先进工艺设计的性 能和市场优势。

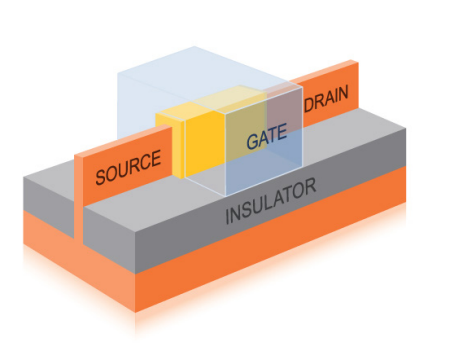

图1. 与传统 CMOS 技术相比,FinFET提供明显更快的开关时间和更高的电流密度(资料来源:GLOBALFOUNDRIES。已获得使用授权)。

点击这里查看完整白皮书

来源:西门子EDA