随着IC芯片尺寸因小型化和快速化的技术需求而越来越紧凑,随着切换速度的不断加快,升降时间下降至亚纳秒量级,这种境界以前只有微波工程师能够企及。而这种无止境的微缩态势挑战着摩尔定律,也给很多老设计带来巨大问题,因为越来越快的切换加剧了信号完整性问题。多年来,随着逻辑驱动器不断加速切换,振铃、串扰和电磁辐射(EMI)的问题也变得越来越严重。

这让大家陷入一个窘境——那么多年一直运作完美的产品,因为使用了一批最新生产的IC,而性能突然变得不可靠了。造成这个问题的原因是上升时间缩短。图1中显示了同一时钟频率在三个不同上升时间时的表现情形。

图1:随着上升时间加快而增加的振铃现象(Hyperlynx仿真分析)

这个例子使我们深切感受到了2个要点。首先,线路设计确定时,加快切换会引发杂散信号,表现为过冲和振铃。这个问题是不可避免的,只能通过改善排列和布线、减少负载数量和/或增加端数量,在一定程度上加以预防。其次,IC制造商使用所谓“新改进的”的逻辑电路,对我们并非一定有好处。新电路用到老设计中,速度的增加造成的结果可能只会让大家头痛。

从IC制造商的角度来看,缩小芯片是一张好牌,因为新芯片几乎肯定能够以更低的成本达到甚至超过其已发布的规格。然而,从设计者的角度来看,在现有的产品设计中缩小芯片可能是冒险之举,前景堪忧,因为新的上升沿和下降沿几乎肯定会速度更快。

更快的边沿速率意味着反射和信号质量问题。因此,即使封装没有改变,时钟速度没有改变,沿用老设计也可能存在问题。驱动器边沿速率的增强对信号质量、定时和串扰有重要影响,也会直接导致辐射干扰。

图2显示了先前讨论到的上升时间从最慢到最快时,辐射的大幅增加。当达到亚纳秒级上升时间,辐射量很容易超过FCC/CISPR B类产品中对无端接传输线的限制。

图2:边沿速率从30ns(左)到1ns(右)时辐射干扰

信号上升时间与互连延时的比值决定了电路如何表现。比值小,意味着当互连延时确定时,上升时间短,从而产生分布;而比值大,则会产生集总,这个很少需要维护。在考虑电路结构的方方面面时,物理尺寸和上升时间之间的关系决定了该对象在电路总体方案中的相对重要性。信号上升时间,而不是信号时钟频率,决定了临界信号速度。基本上,上升时间在1ns以内,须加以关注。

一个理想的方波信号占空比为50%,上升时间为0皮秒,频率分量(谐波)应是时钟频率的整倍数。傅里叶变换把时域波形转换为对应的频域中的正弦波频谱。偶次谐波的振幅为零,因为占空比的原因在傅里叶变换中抵消了。奇次谐波的振幅计算公式: V(谐波)=2/πn

其中n是谐波数,为奇数

例如,第1次谐波的振幅,即 n = 1,2 /(3.14×1)= 0.64V;第3次谐波的振幅,n = 3,2 /(3.14×3)= 0.21V。因为谐波频率逐次升高,而谐波振幅随着频率升高反而会减弱。图3显示了一个时钟信号的奇次谐波从理想的1GHz,上升到100GHz,其振幅计算情况。

然而,在实际应用中,信号上升时间对最大信号带宽有直接影响。说到频带,这个真的很重要,对数字设计尤其重要。我们习惯使用0.35/Tr作为有效带宽(其中Tr是上升时间,单位为ps)。然而,有一个更准确的方法是使用0.5/Tr作为截止频率,可以在时域和频域之间形成一个简单却有效的对应关系。例如,如果上升时间为500ps(目前普遍如此),那么不管时钟频率是多少,有效带宽实际上是1GHz。可能会有2种不同的波形,它们有相同的时钟频率,但上升时间和带宽却不同。

图3:1GHz开始的时钟信号的奇次谐波

当选择最适合设计的介质材料时,应考虑到第5次谐波的带宽。互连线的带宽是指可以通过互连线传输且损耗不是很大时的最高正弦波频率。我们以1GHz为例,如果上升时间未知,要考虑的最大带宽是第5次谐波时的5GHz。

FR-4,一种环氧玻璃材料,常用于多层印制线路制造,频率在1GHz以下时损耗可以忽略不计。但由于介质损耗的频率依赖性,在频率较高时,FR-4的介质损耗增加。因此,做高频数字、射频和微波设计时,需要考虑使用更低损耗的替代材料。(为了便于大家选择,可以查阅iCD介质材料库,有31,000种以上的刚性和挠性材料可供选择,工作频率可达100GHz。)

电磁辐射来自信号的每个频谱成分。对于较差的共模电流,辐射干扰将随频率线性增加。虽然谐波振幅随频率升高逐次下降,但辐射的能力呈线性增加,因此所有的谐波对电磁干扰都一样难辞其咎。为了减少电磁干扰,设计目标是在确保一定的数据传输量的同时,使用尽可能低的带宽。

高频谐波会和平面振子发生谐振,因为频率接近半波长而产生波浪效应,在极端情况下,这可能导致整个系统发生故障。这就是为什么解决信号完整性问题最好要从降低电磁干扰开始。

图4:FPGA时钟的串联端电阻(来源:iCD Design Integrity)

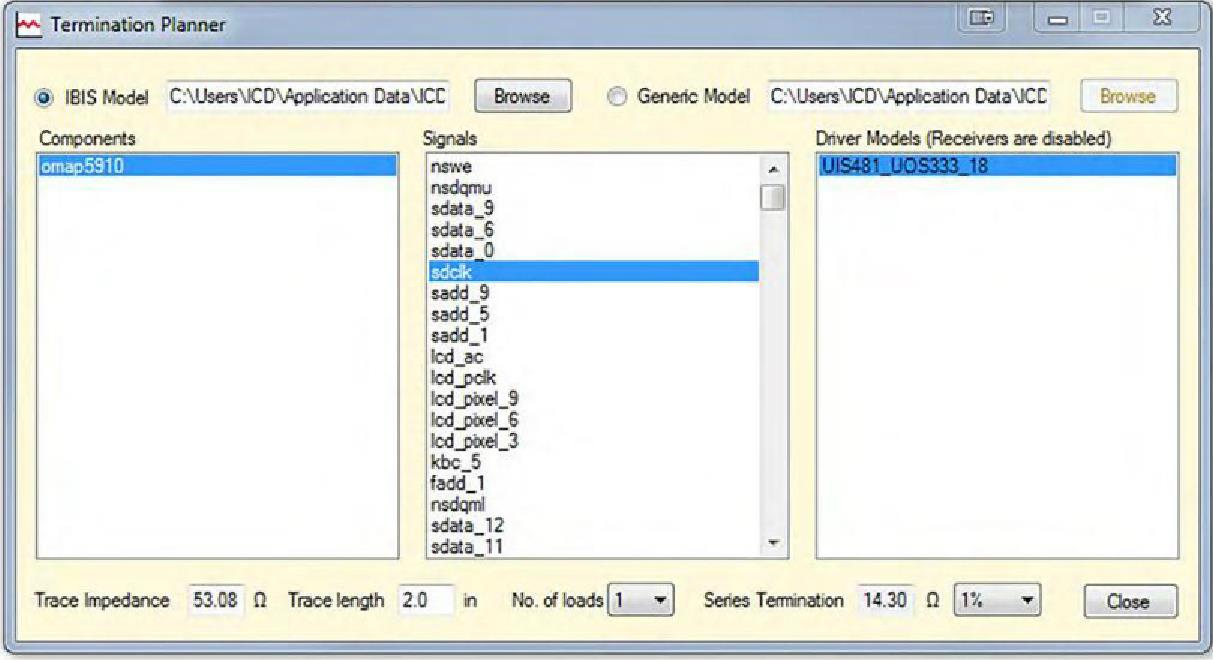

为了提高信号完整性,抑制电磁干扰,需要减慢信号的上升时间,以减少高频分量。通过在信号源端将终端电阻与传输线串联起来,就很容易做到这一点。在IC IBIS模型中,选取IV曲线,然后基于分布式系统计算出所需的串联端电阻,以匹配所选层的传输线,如图4所示。因此,要修复出现间歇性故障的老产品,只需添加一个串联电阻即可。事实上,有一个聪明的做法,在关键的互连线中增加一个0欧姆电阻,这样可以为未来设计需要加入串联电阻时预留好空间。

牢记以下要点:

- 加快切换会引发杂散信号,表现为过冲和振铃。这也直接导致辐射干扰。

- 已有产品因为使用了一批新生产的IC,性能突然变得不可靠。造成这个问题的原因是上升时间缩短。

- 即使封装没有改变,时钟速度没有改变,沿用老设计也可能存在问题。

- 当达到亚纳秒级上升时间,辐射量很容易超过FCC/CISPR B类产品中对无端接传输线的限制。

- 信号上升时间与互连延时的比值决定了电路如何表现。

- 一个理想的方波时钟信号只有在时钟频率的奇数倍时才有频谱分量。

- 在实际应用中,信号上升时间对最大信号带宽有直接影响。

- 使用5/Tr作为截止频率,可以在时域和频域之间形成一个对应关系。

- 当设计时选择最适合的介质材料,应考虑到第5次谐波的带宽。

- 做高频数字、射频和微波设计时,需要考虑使用更低损耗的替代材料。

- 高频谐波会和平面振子发生谐振,产生波浪效应,导致整个系统发生故障。

- 解决信号完整性问题最好要从抑制电磁干扰开始。

- 为了提高信号的完整性,降低电磁干扰,需要减慢信号的上升时间,以减少高频分量。通过在信号源端将终端电阻与传输线串联起来,就很容易做到这一点。

- 有一个聪明的做法,在关键的互连线中增加一个0欧姆电阻,这样可以为未来设计需要加入串联电阻时预留好空间。

参考文献:

- Barry Olney’s Beyond Design columns: Material Selection for SERDES Design, Mastering ‘Black Magic’ with Howard Johnson’s Seminars, Signal Integrity Part 1, New Functionality Improves Designer's Productivity, Plane Crazy Part 2.

- Eric Bogatin, Signal and Power Integrity Simplified, Bandwidth of a signal from its rise time

- Howard Johnson, Martin Graham. High-speed Digital Design.