PCB设计师持续面临的挑战之一是产品尺寸越来越小。但随着高密度互连(high-density interconnect,简称HDI)结构的普及,或多或少缓解了由外形因数导致的设计压力,与传统PCB相比,HDI能在单位面积内实现更多的功能。HDI通过更精细的走线、更薄的材料和激光钻通孔,在设备微型化进程起着重要的作用。传统PCB减成法蚀刻工艺很难生产出3mil以下的线宽、线距,使PCB设计随着电子封装尺寸的缩小而变得越来越复杂,添加额外的布线层和微导通孔层,增加必要的层压周期次数,而这些方法也会对良率、可靠性和成本产生影响。

随着智能手机技术进入5G时代,HDI生产技术得到了发展。输入、输出天线结构变得越来越多,RF前端也变得越来越复杂,导致RF组件的占位越来越大。5G固有的更高带宽要求更严格的阻抗控制。如果不能通过精密控制线路,HDI上较细的走线可能增加信号衰减风险。为了满足这些要求,5G智能手机内的HDI上可使用的空间大幅减少。

半加成法工艺(semi-additive process,简称SAP)是在生产超精细走线电路时用于降低积层材料耗散损耗(Df)的成熟生产方法。该方法利用了加成法工艺步骤,在基底介质材料上添加铜,而不是用减成法工艺构建电路图形。在此之前,制造商只能生产出3mil的线宽、线距,但使用SAP工艺后可以可靠地生产出1mil以下的线宽、线距。若想进一步减小尺寸,就需要采用IC载板制造行业常用的各种SAP制造工艺了,其中包括激光直接成像(LDI)技术、改良后的激光钻孔技术、超薄铜箔、导通孔填充全板电镀,以及闪蚀技术,融入了这些技术的工艺称之为改良SAP(modified SAP,简称mSAP)。

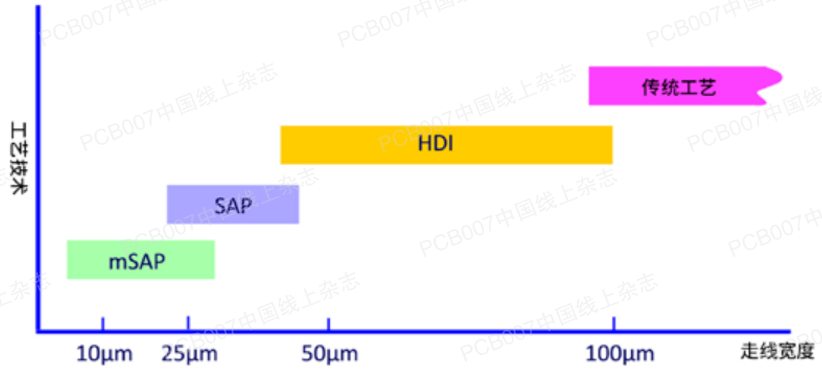

SAP使PCB制造商能够使用加成法丝印技术而无需用去除边缘的蚀刻工艺,最终可以大幅减少面积、减少层数及电子产品质量,并可提供很多有益于RF技术的优势。图1展示了现有技术工艺及其对应的走线宽度。

图1:走线宽度与工艺技术对比

智能手机、平板电脑和可穿戴设备市场促进了mSAP工艺的发展,使其已能应用于大批量PCB生产。目前的设计融合了减成法蚀刻工艺和mSAP工艺。这种技术组合对于更薄、尺寸更小的母板设计起到至关重要的作用,这种设计可以为更稳健的电池释放出更多空间。对第11代iPhone X进行技术拆解,会发现其中的线宽、线距设计为1.2mil(30μm),而更高阶的设计拥有0.4mil(10μm)的特征。这种工艺完全颠覆了PCB设计。

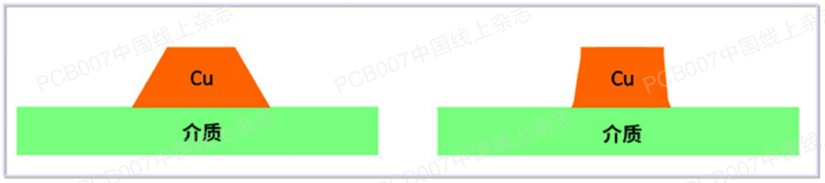

SAP可以更严格地控制走线宽度并可加工出垂直的导体侧壁,大幅提升阻抗控制。在减成法工艺中,需要先在铜层上涂覆一层抗蚀剂涂层,然后再蚀刻去除不需要的铜,留下需要的铜形成精细的走线。这种方法的最大缺点就在于垂直蚀刻走线所使用的化学蚀刻剂也会溶解掉走线侧壁上的铜。在剖面示意图中能看到蚀刻后的走线是梯形的(图2)。

图2:减成法工艺(左)和加成法工艺(右)形成的走线图形

而使用SAP技术,只需在层压板上涂覆非常薄的铜层,然后电镀没有涂布抗蚀剂的区域即可。随后再蚀刻去除导体间还残留的薄铜。这种方法可以蚀刻出导体侧壁垂直的走线,精度非常高,走线剖面几乎呈矩形,最大程度地提高了电路密度,实现了精确的阻抗控制,降低了信号损耗。使用传统的减成法蚀刻工艺时,受控阻抗的容差通常规定为±10%,这是因为材料和工艺都存在偏差。而使用SAP,可以更精确地控制走线宽度容差,受控阻抗也可以遵循更加严格的规定容差。

标准SAP工艺通过粗化或纹理化介质基板达到足够的附着力,但电镀树脂界面处粗糙的表面有可能在高信号速度下增加传输损耗。为了改善高频信号传输的信号完整性,SAP工艺应该使镀层与树脂界面处具有高附着力,同时又可保持界面比较光滑。因此,铜层粗糙度应该保持在1µm以下。

BGA球栅接触焊盘之间的间距越来越小,因此布线通道受到的限制越来越多。一些FPGA供应商了解PCB设计师在布线信号时面临的挑战,所以一直保持着0.30mm的接触焊盘直径,从而最大程度地增加电路板外表层上的导体布线通道。尽管智能手机和平板电脑的尺寸已经稳定,现在的趋势是朝着系统级封装发展而不是进一步缩小尺寸。未来我们必会见到间距为0.3 mm或以下的更多芯片。

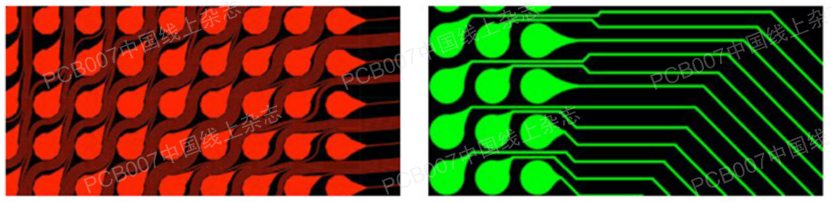

一般情况下,PCB设计师通过HDI技术只能布线到BGA四周最靠外的两行焊盘。多年来,针对一般低成本多层板的布线底线,有一条不成文的规定是不能挤压BGA焊盘之间的一条信号走线或扇出导通孔。但只要你愿意多花钱,这个底线也可以拉伸到如图3所示(右)。但SAP工艺保证了更大的自由度,能够在焊盘之间形成6个1/1mil的线宽、线距。图3(左)是在间距为0.3 mm的焊盘之间布多条走线的示意图。但这种工艺也在接近极限,其原因并不是物理尺寸,而是因为信号完整性对阻抗和耦合有要求高。紧密布线的信号走线会存在一些问题:

图3:SAP工艺(左)与HDI布线(右)对比(来源:Averatek)

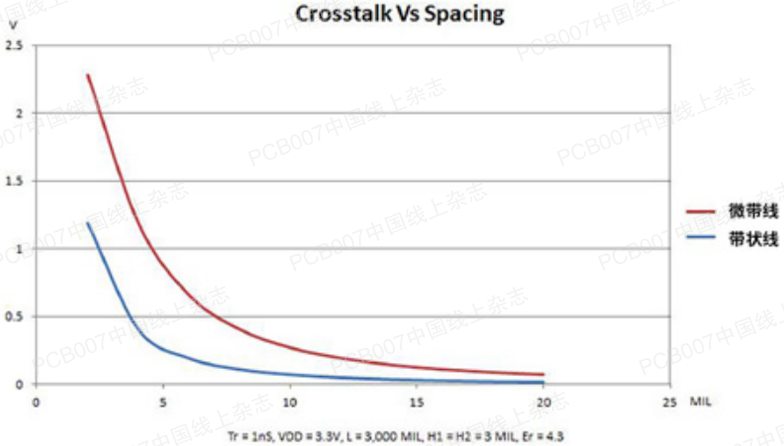

在1mil间距的走线之间,平行段之间非有意的耦合效果极强。也许分组的同步总线和数据通道还能承受这种强度,但对于不相关的信号而言却是难以容忍的。图4所示是紧密耦合后出现的串扰呈指数增长,特别是外部的微波传输带层。

图4:微带线和带状线层之间的间距变化及其导致的串扰对比

走线的阻抗大小必须维持在40~50欧姆之间,决定了无法用HDI叠层的标准介质厚度满足该要求。1mil或以下的极薄介质需要保持1mil走线具有50欧姆的阻抗;但该技术可能不适用于标准HDI刚性板。但是Apexyl LPEN/LPET、Dupont Pyralux Flex、ThinFlex A/H、Ultrflex GTS 7800以及Rogers R/Flex Crystal和Jade材料均可提供厚度为1mil的低损耗挠性材料,可形成理想的挠性电路。

除非能在顶(元件)层完成所有走线的布线,否则仍需要扇出导通孔。使用焊盘内导通孔和盲孔可以大幅减少所需要的板面面积。

半加成法工艺在信号完整性方面也具有显著的信号完整性优势。走线宽度更加可控,再加之垂直的导体侧壁,大幅提升了阻抗控制。与此同时,SAP还可以通过减少环面积和增加密度的方式来降低寄生电感。使用SAP技术还可以实现具有精细走线精度的RF特征。

3D打印PCB也是加成法工艺。3D打印技术可实现任意的产品外形,有助于人们找到新颖的解决方案来解决难题,从而实现新的产品设计。从数字设计到生产出来的成品,整个过程可以做到一站式无缝工艺。同时还可以打印3D天线、线圈,并消除损耗发生器。尽管3D打印目前能打印的最小线宽、线距为3/4mil,但对于样品生产而言具有巨大的优势,只需几个小时在公司内部就能生产出多层板。

关键要点:

- 随着高密度互连技术的普及,由外形因数导致的设计压力得到了部分缓解。

- 传统PCB减成法蚀刻工艺很难生产出3mil以下的线宽、线距。

- HDI的走线越薄,就越有可能增加信号衰减风险。

- SAP是可以用于生产超精细走线电路积层材料的成熟生产方法。

- 在SAP出现之前,制造商只能加工出3mil的线宽、线距,但现在SAP可以可靠地生产出1mil以下的线宽、线距。

- 若想进一步缩小线宽、线距,则需要采用各种mSAP制造工艺。

- SAP可使PCB制造商使用加成法丝印技术,无需去除边缘的蚀刻工艺。

- SAP可以更严格地控制走线宽度,实现垂直的导体侧壁,大幅提升阻抗控制。

- 与传统的减成法蚀刻工艺相比,SAP能提供更加严格的阻抗容差。

- SAP工艺可在焊盘之间形成6个1/1mil的线宽、线距,可增加布线密度。

- 在1mil间距的走线之间,平行段之间非有意的耦合会非常强。

- 1mil及以下的极薄介质需要保持1mil走线具有50欧姆的阻抗。

- 尽管使用焊盘内导通孔和盲孔可以大幅减少所需的板面面积,但SAP工艺仍需要用扇出导通孔。

更多内容可点击这里阅读原文查看,文章发表于《PCB007中国线上杂志》22年5月号,更多精彩原创内容,欢迎关注“PCB007中文线上杂志”公众号。