数字电路的电磁辐射可以以差模或共模的形式出现。差模通常是相等并且相反的,因此所有的辐射场都会相互抵消。相反,来自2个耦合导体的共模辐射是相同的。它不会互相抵消,而是互相增强。

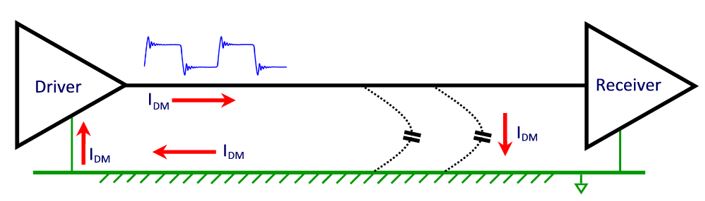

但是,差模传播会在遇到寄生电容、信号时滞、上升/下降时间不匹配、信道不对称引起的不平衡时转换为共模。还有返回路径不连续也会产生很大的共模回路区域,这会增加串联电感和电磁辐射。在本月的专栏中,我将探讨共模辐射的常见“症状”,并提出一些“治疗”方法。

差模辐射会随着正常的电路工作发生,它是电流通过由PCB导体(迹线和参考平面,如图1所示)形成的返回路径回路的结果。微带线(外层)回路可以被看成主要辐射磁场的小型天线,而带状线(内层)回路仅从PCB边缘的边缘场发射辐射。尽管这些信号回路对于电路工作是必须的,但在设计过程中,必须对它们的尺寸和回路面积进行控制,以使辐射最小化。

图1:正常(差模)信号返回电流

幸运的是,没必要针对每个回路都进行评估,只需要对最关键的回路进行分析就可以了。其他的回路可以通过良好的叠层设计方法进行控制。更多信息,可以参阅我的专栏文章《超越设计:叠层计划》第1~4部分[1]中的指南。

最关键的回路通常是频率最高、周期性信号的回路。在同步电路中,时钟信号是会产生最多辐射的重复脉冲序列。时钟信号应该最先布线,尽一切努力将它的回路面积缩到最小。时钟信号布线长度应该尽可能短,层转换导通孔的数量也要尽可能少。在多层PCB上,时钟信号应放在紧挨着整块参考平面的带状线(内层)上,以减少辐射。时钟布线和返回平面之间的间距应尽可能小,以增加耦合并减小回路面积。此外,为了防止时钟耦合到要离开PCB组件的线缆上,时钟电路应该远离I / O连接器和线缆。

数据和地址总线以及相关的命令和控制信号排在这个关键列表中的第二位。这些总线通常有终端电阻,可以传输较高的峰值电流,而发出的辐射与传输的电流大小成正比。瞬态供电电流是差分辐射的另一个重要来源。虽然这些回路可能非常小,但它们可能会在开关过程中传输大电流。

差模辐射与频率的平方成正比,可以通过将电源分配网络(PDN)的阻抗降低至所需目标阻抗

以下、最小化回路面积、使用差分信号消除场以及时钟抖动来控制。如果发射的幅度在频带中是分散的,那么辐射也会减小。扩频时钟最多可以减少15dB的辐射。

图2:差模信号有可能会转变成共模

在平衡良好的差分对中,紧密耦合将可实现有效的场抵消。但是,如果它们不完全平衡(图2),那么消除的程度就不是由间距决定的了,而是由差分对的共模平衡决定的。大多数数字驱动的共模平衡都较差,这就会造成差分对的共模功率比差模功率大得多。在这种情况下,将差分布线更紧密地耦合在一起不会减少辐射。图3展示了一个仿真的不平衡差分对在参考平面中的共模返回电流的截面图。

紧密耦合的差分信号主要工作在差分模式下,其中一些共模辐射来自信号中的不平衡。如果为了防止耦合,两条布线的距离足够远,那么它们都会变成单端信号,100欧姆的差分对就会变成两个单独的50欧姆单端信号。只要回路面积小并且阻抗不会沿信号长度变化的话,这也没有什么问题。

图3:耦合的微带线差分对(来源:Ansoft)。

相反,作为“反面角色”的共模辐射,是由于导体中不需要的电压降而引起的电路寄生现象的结果。当信号沿传输线传输时,布线和平面导体之间的电容耦合构成了回路,位移电流流过电容,返回到源(图4)。流过接地阻抗的共模电流在数字逻辑地系统中产生电压降,并产生磁辐射。

图4:共模信号返回路径

更糟糕的是,当有线缆连接到PCB上时,它们会形成天线,被这种共模地电位激励。实际上,100MHz信号在1米长的线缆上,仅需3uA的共模电流即可达到FCC B级电磁兼容(EMC)测试的上限。差模辐射可以通过叠层设计和布线进行控制,但共模辐射可能更难于理解和控制,因为它是无意中设计到系统中的。原理图并不会显示任何对我们理解信号性能、串扰和电磁辐射至关重要的激进电流路径。

共模辐射中,最普遍的是来自系统的线缆,其起到偶极或单极天线的作用。因此,限制共模电流很重要:

- 减小电流和电源电压;

- 减少电流上升时间、频率和谐波含量;

- 缩短天线长度;

- 加入与线缆串联的共模阻抗扼流圈,并尽可能使用变压器或光耦合器将线缆与PCB隔离;

- 屏蔽线缆并分流其电流。

不能允许PCB电源层延伸到I / O连接器的接地区域。这是由于电源层通常包含高频开关噪声,如果延伸到I / O区域,可能会将噪声耦合到I / O信号和地中。这里的关键是I / O的地和机壳的地之间通过唯一一个非常低阻抗的点连接。

此外,在PCB上,一旦微带线短柱(Stub)长度接近四分之一波长,就会变成天线。这些短柱会成为非常高效的发射器,因此最好避免。在采用DDR3 / 4 fly-by架构的多点总线中,可以通过将信号线路直接排布成通过每个存储器件的焊盘来避免短柱。

控制共模辐射时,重要的一点是在噪声源处尽量减少激励天线的共模接地电压。PDN噪声是辐射的主要来源。可以通过阻止噪声从处理器转移到电源层和接地层,以及设计一个能够在直到最大带宽都有低于所需目标AC阻抗的PDN来最小化PDN噪声。低阻抗PDN可以通过最小化电源层和接地层之间的间距,以及以低电感方式安装在电源和接地层上的低阻抗去耦电容来实现。建议使用PDN Planning工具来对复杂的要求进行有效分析。

此外,良好的接地通过给共模电流提供一条到地电位的低阻抗路径来降低噪声源。在叠层中使用多个地平面是实现这一点的非常有效的方法。在这里,我再次强调在完整平面中避免插槽或分裂的重要性。

如果共模电流的返回路径远离信号路径,那么共模电流就会产生辐射。但是,如果将返回路径设计为接近源电流,那么回路面积就会很小,共模电流就不会辐射。因此,不是所有的微带线都会辐射——只有设计不佳的才会。

关键点:

- 差模辐射相等且相反,因此辐射场会相互抵消;

- 来自2个耦合导体的共模辐射是相同的,它不会互相抵消,而是互相增强;

- 微带线回路可以被看成主要辐射磁场的小型天线;

- 带状线回路仅从PCB边缘的边缘场发射辐射;

- 最关键的回路通常是频率最高、周期性时钟信号的回路;

- 时钟信号应放在紧挨着整块参考平面的带状线(内层)上,以减少辐射;

- 时钟布线和返回平面之间的间距应尽可能小,以增加耦合并减小回路面积;

- 差模辐射可以通过减小电源分配网络(PDN)的阻抗、最小化回路面积、使用差分信号消除场以及时钟抖动来控制;

- 如果差分对没有完全平衡,那么抵消的程度就不是由间距决定的了,而是由差分对的共模平衡决定的;

- 紧密耦合的差分信号将主要在差分模式下工作,其中一些共模辐射来自信号不平衡;

- 如果2个差分信号距离足够远能够不发生耦合,那么它们都会变成单端信号;

- 共模辐射是由于导体中不需要的电压降而引起的电路寄生现象的结果;

- 当有线缆连接到PCB上时,会形成天线,被这种共模地电位激励;

- 由于可能会将噪声耦合到I / O信号和地中,因此不能允许电源层延伸到I / O连接器的接地区域;

- 一旦微带线短柱(Stub)长度接近四分之一波长,就会变成天线;

- 可以通过将信号线路直接排布成通过每个存储器件的焊盘来避免短柱;

- 控制共模辐射时,重点是在噪声源处尽量减小激励天线的共模接地电压,而PDN噪声是辐射的主要来源;

- 低阻抗PDN可以通过最小化电源层和接地层之间的间距,以及以低电感方式安装在电源和接地层上的低阻抗去耦电容来实现。

参考资料

- Barry Olney’s Beyond Design columns:Return Path Discontinuities, Uncommon Sense-Differential Pairs, Stackup Planning Parts 1-4.

- Electromagnetic Compatibility Engineering, by Henry Ott.

- What is Differential and Common-Mode Current? by Ron Brewer.

- Understanding Common-Mode Noise, by Pulse Electronics.

- High-Speed Signal Propagation, by Howard Johnson.

Barry Olney是澳大利亚In-Circuit Design Pty Ltd(iCD)的总经理,In-Circuit Design是一家专门从事板级模拟的PCB设计服务机构。该公司开发了iCD Design Integrity软件,包括iCD Stackup、PDN和 CPW Planner。该软件可以从www.icd.com.au下载。联系Olney或阅读往期专栏,请点击此处。