作者:Barry Olney

(澳大利亚In-Circuit Design Pty Ltd (iCD)公司执行董事。该公司深耕PCB设计服务领域,专门研究线路板级模拟技术,其研发的iCD Design Integrity 软件整合了 iCD Stackup、PDN和CPW Planner。)

PCB设计领域的技术发展日新月异,不论设计师是否具备丰富的从业经验,对他们而言,目前这种状况既为他们创造了机会也对他们提出了挑战。PCB设计师必须处理各种各样的问题,在PCB形状因数、功能性和功率要求之间找到恰当的平衡,同时还要确保线路板上的叠层、布局和布线完整,保证严格的信号质量和功率质量。如果想用更短的周转时间制造出紧凑、灵活、高性能、低功率的PCB,就需要高阶工具并掌握更先进的技能。还有一种趋势是在基于云的平台上创建团队合作环境,设计师和制造商在平台上协作,确保设计可靠且可制造。

随着多层PCB变得越来越复杂,PCB设计师面临的挑战是要把越来越多的元器件和连接结构塞入有限的板面内,同时还不能影响PCB的性能表现和质量。增加信号层层数有助于增加信号布线容量并减少干扰,但对于引脚数较多器件的引线扇出,存在不可避免的瓶颈。使用高密度互连、盲孔、埋孔和焊盘内通孔结构有助于减轻这些问题。

球栅阵列封装(Ball grid array,简称BGA)封装有各种各样的间距和尺寸。随着器件复杂程度的不断增加、OEM不断推动元器件缩小,0.5mm或以下的球间距变得越来越受欢迎。如今,每部智能手机的BGA间距都已经降到了0.4mm,下一代超细间距BGA的球栅间距将达到0.3mm。下一步要做的就是在相同的封装内增加更多功能。早期用户已经开始尝试使用0.3mm间距的BGA器件。但目前还没有正式推出专门针对0.3mm间距的IPC设计指南或布局准则。因此,许多PCB设计师在开发基于新的0.3 mm间距器件的设计时会很大程度地依赖针对0.5mm间距的设计指南和布局准则。比如现在的设计指南允许使用直径比BGA/CSP焊料球小20%的BGA/CSP焊盘。

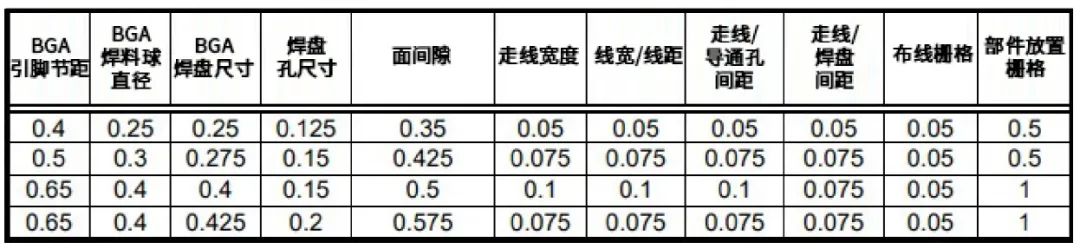

表1:常见BGA特征尺寸(来源:PCBLibraries)

表1展示了BGA的规定特征尺寸实例。依照这个表格,我们可以确定扇出细间距BGA焊料球所需的信号层层数。一旦知道了BGA上信号的位置,就可以估算出布线特定设计时所需的最少信号布线层层数。

- 前两行/列会布线在第一层信号层

- 第二个两行/列将布线在第二层信号层

此外,超过4排后,每排信号球栅通常都需要额外的信号层。

假设所有焊料球都已布线,把它们连接在一起可传递信号。但如果一些焊料球未连接,那么那些相应的焊料球逃逸通道对于其他信号是空闲的。这样的话,如果所需信号有足够畅通的布线通道,那么更少信号层就已足够。0.5mm或更小间距BGA的扇出通常需要用盲孔和焊盘内导通孔。

为BGA提供大量独立电源也是问题。根据BGA扇出,通常可以在每个电源层上放置3~4个电源。因此,10个电源加接地通常需要4个电源层。如果混合层上既有电源又有信号,则可以减少电源层。

随着数据传输速率的提高,数据传输所需的带宽也随之增加,导致PCB设计出现了信号完整性、串扰、阻抗匹配和电磁干扰等方面的新挑战。PCB设计师还必须在PCB层数和制造复杂性之间做出权衡。例如,如果平行走线段的长度超过12mm且上升时间为200ps,则信号完整性要求也可能影响设计师的权衡。

PCB设计是一项复杂、极具挑战的工作,设计师需要考虑到可能影响PCB性能和质量产生的各个方面,其中信号完整性、电源完整性、热量管理和电磁兼容性是确保PCB功能性和可靠性的关键因素。PCB设计师需要掌握更多知识和技能,应用恰当的原理、方法和工具才能分析并优化PCB设计的这些方面。

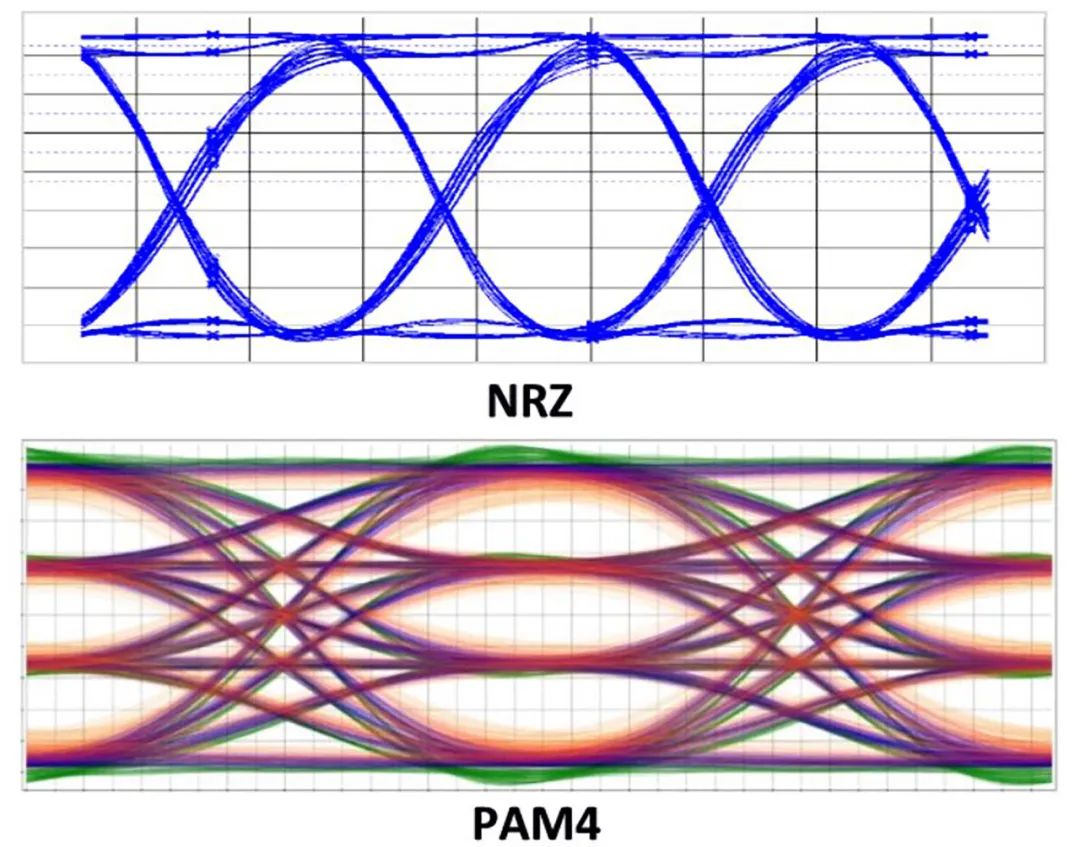

数据传输速率提高以后,还需要更复杂的数据编码调制方案,例如不归零编码 (non-return-to-zero,即NRZ) 和四电平脉冲幅度调制编码(pulse amplitude modulation 4-level,即PAM4)。这些方案使用信号的多个电平或相位来编码每个符号的更多位,从而提高信道的频谱效率和数据传输速率。然而,这些方案也增加了信号处理和恢复电路的复杂性和灵敏度,需要设计师在设计PCB时非常谨慎,确保适当的信号质量和信号同步。NRZ是一种调制技术,它用两个电压电平来表示逻辑信号0和逻辑信号1。而PAM4使用4个电压电平来表示2位逻辑信号的4种组合——11、10、01和00(图 1)。

图1:NRZ眼图与PAM4眼图(来源:Xilinx)

阻抗是控制设计稳定性的关键因素,也是信号完整性方法论的核心问题。应通过场解算器模拟阻抗,从而获取基板上每个信号层的准确阻抗值。走线的阻抗值非常重要,因为传输路径上的任何不匹配都会导致信号质量下降并可能出现噪声辐射。为了保证良好的能量转移,源端的阻抗值必须等于负载端的阻抗值。

但实际情况并非如此,通常需要快速的边沿速率终止传输来限制振铃效应。如果此噪声未在源端受到限制,就会耦合到附近的受扰走线上形成串扰并发生辐射,产生更多EMI。除了EMI、信号完整性和串扰问题外,这种噪声还会由于时序故障和干扰而导致产品间歇性运行,从而大大降低产品的可靠性。过度的振铃效应还会导致电源完整性问题。

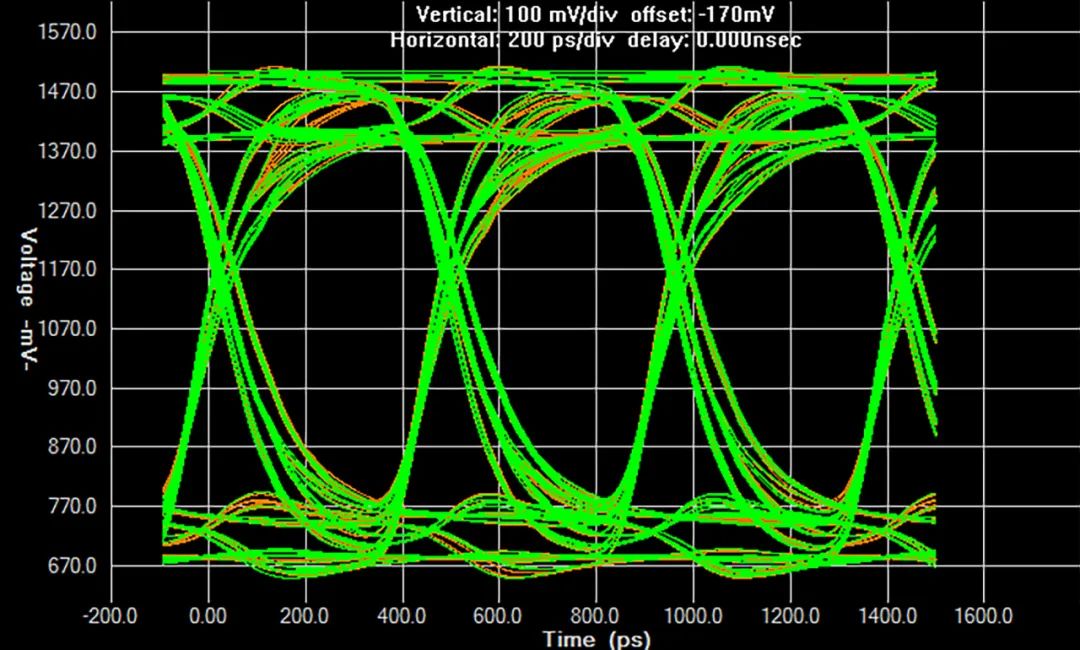

飞行时间延迟和偏差是引起高速PCB设计信号完整性问题的重要因素。影响飞行时间和时间偏差性能的因素之一是元器件的放置位置。在经典的高速设计流程中,会对时序规范模拟结果进行对比,从而确定元器件旋转和布线的限制条件。在给定的长度限制内,设计人员可以通过控制接口各个部分的PCB走线拓扑结构来控制信号完整性。此拓扑中包括任何端接。图2展示了由于端接不良而导致信号抖动和振铃的眼图。

图2:端接不良的信号眼图

PCB叠层和PDN的完整性是一款性能稳定产品的基础。多层PCB设计正变得越来越复杂且容忍度越来越低,影响因素已经不仅仅局限在信号完整性、串扰和EMI了。基板和电源传输系统极其关键,如果这两部分发生故障,那么整个系统可能都会崩溃,最坏的情况则可能只是间歇性地工作。

如今的高性能处理器采用了具有高瞬态电流和高时钟频率的低直流电压,以最大限度地降低功耗,从而减少散热量。一般的高速设计包含10个或以上独立电源。不幸的是,更低的核心电压、更高的电流和更快的边沿传输速率都会影响电源分配网络 (power distribution network,即PDN) 设计和信号完整性。

理想情况下,PDN的有效阻抗值应保持在目标阻抗值以下,直至最大所需带宽。但如果阻抗值远低于目标值,则意味着PDN设计过度,徒增了不必要的成本,却几乎没有增加收益。通过这种方式,如果贵公司打算生产数十万个组件,那么潜在的成本节约可能会非常可观。分析PDN可以确保以成本效益最高的价格获得最佳的性能。

许多能力出色的PCB设计师将在未来几年内退休,他们掌握的知识也随着他们一同消失,技艺纯熟、经验丰富的PCB设计师变得越来越紧缺,需要更多新入行的年轻PCB设计师补充缺口。同时,PCB设计师之间要有更多协作和创新的机会。然而,若即将上岗的设计师缺乏制造相关知识,他们设计出的产品就会出现错误和故障,这样就会增加设计时间和成本,并降低产品的可制造性和良率。

经验是最好的老师。PCB设计师需要掌握更多的知识和技能,才能设计出具有高信号完整性、电源完整性、热性能和电磁兼容性的PCB。PCB设计师必须了解用于分析和优化PCB设计各个方面的原理、方法和工具。

关键要点

- PCB设计师必须处理各种各样的问题,要在PCB形状因数、功能性和功率要求之间找到恰当的平衡。

- 间距为0.5mm及以下的BGA变得越来越受欢迎。

- 下一代超细间距BGA的间距是0.3mm,且在相同的封装内会增加更多功能性。

- 目前还没有开发出专门针对0.3mm间距的正式IPC设计指南或布局规则。

- 0.5mm或更小间距BGA的I/O扇出通常需要用到盲孔和焊盘内导通孔。

- 为BGA提供大量独立电源也是问题。

- 数据传输速率提高后,还需要更复杂的数据编码调制方案,例如不归零制 (non-return-to-zero,即NRZ) 到四电平脉冲幅度调制编码(pulse amplitude modulation 4-level,即PAM4)。

- 应通过场解算器模拟阻抗,以获取基板上每个信号层的准确阻抗值。

- 飞行时间延迟和偏差是引起高速PCB设计信号完整性问题的重要因素。

- PCB叠层和PDN的完整性是性能稳定产品的基础。

- 如今的处理器需要用到较低的核芯电压,所以需要用到更高的电流和更快的边沿传输速率。

- PDN的有效阻抗值应保持在目标阻抗值以下,直至达到最大所需带宽。

- 如果阻抗值远低于目标值,则意味着PDN设计过度,徒增了不必要的成本,却几乎没有增加收益。

资料来源

- Beyond Design by Barry Olney: “Fly-over Technology: When It All Gets Too Fast,” “Signal Integrity (Parts 1 & 3),” “The Target Impedance Approach to PDN Design.”

- AM57xx BGA PCB Design, Texas Instruments.

- “Metric Pitch BGA and Micro BGA Routing Solutions” by Tom Hausherr.

欢迎扫码关注我们的微信公众号

“PCB007中文线上杂志”

点击这里即可获取完整杂志内容。