在如今不断小型化的电子设计领域,具有极精细节距特征的BGA部件越来越受欢迎。随着这些细节距BGA复杂性和用户I/O(焊料球数量)的不断增加,寻找逃逸布线和扇出模式的难度也在逐步增加。此外,随着硅几何尺寸的缩小,通道长度会更小,导致了信号完整性问题增加,需要重新探究和/或调整一些传统的BGA逃逸布线方法,不仅能够使BGA设计的I/O成功扇出,而且能够使BGA设计的电路成功运行。

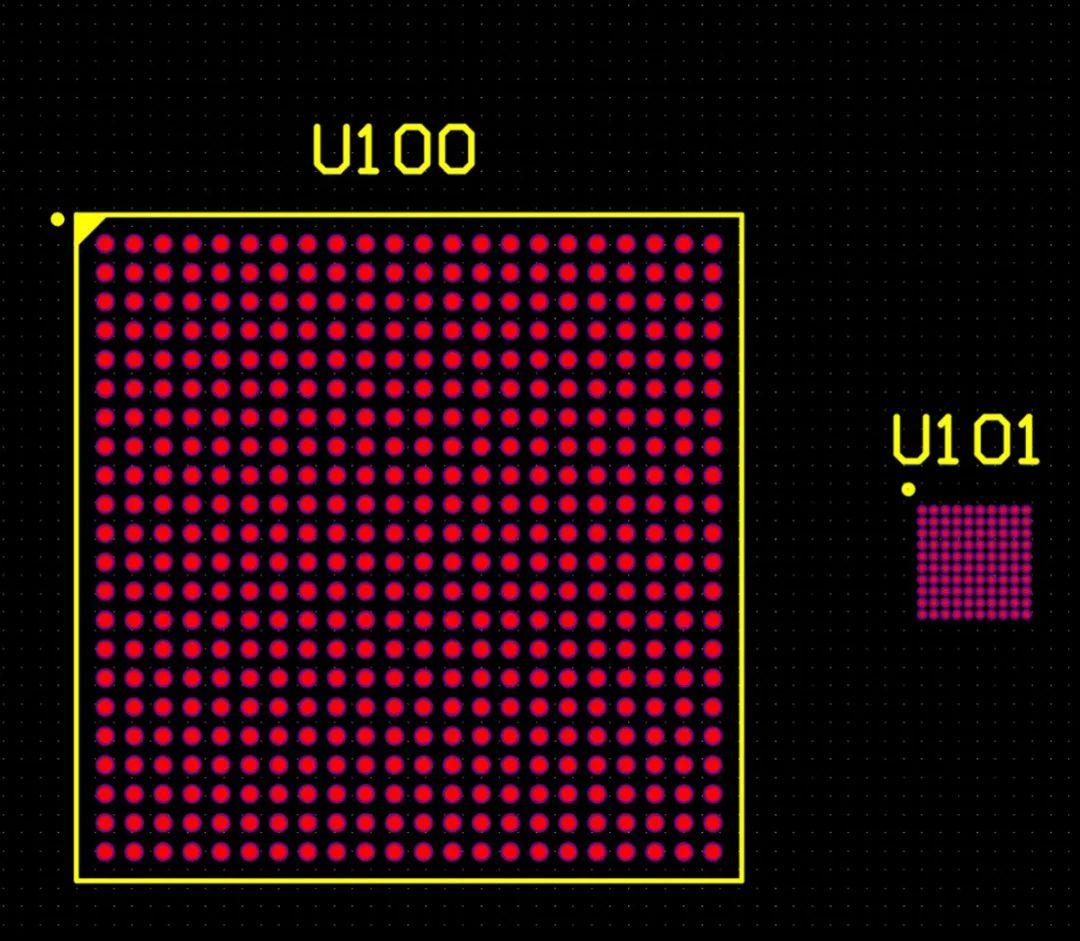

过去可以使用传统的全贯穿通孔结构布线BGA,采用离开BGA焊盘的狗骨状走线。这些BGA的节距通常为1.27 mm,且焊盘之间有足够的间隙,可以在不违反任何设计规则的情况下放置3级产品要求的A级通孔。此外这些封装的特征尺寸可用1盎司铜制造,不会产生任何问题。随着芯片复杂度和I/O密度的增加,目前大多数BGA封装的节距都在1 mm以下,有些封装的节距甚至小到0.4 mm。由于这些更精细节距的BGA封装,无法在BGA下使用传统的全贯穿通孔结构。反过来,需要使用多次层压和微通孔结构,以便成功地逃逸布线BGA。图1对比了具有484个焊料球、1mm节距BGA(U100)和具有100个焊料球、0.4mm节距BGA(U101)的封装和特征尺寸。

图1:具有484个焊料球、1 mm间距BGA (U100)和具有100个焊料球、0.4 mm间距BGA (U101)的封装和特征尺寸的对比

首先,我们来看1mm节距的部件,然后评估如何将所有焊料球逃逸到BGA的外围。对于该评估,只考虑使用堆叠微通孔。交错排布微通孔也可以,但显然需要更大的电路板面积。此外,叠层将为所有内部信号层采用双带状线。

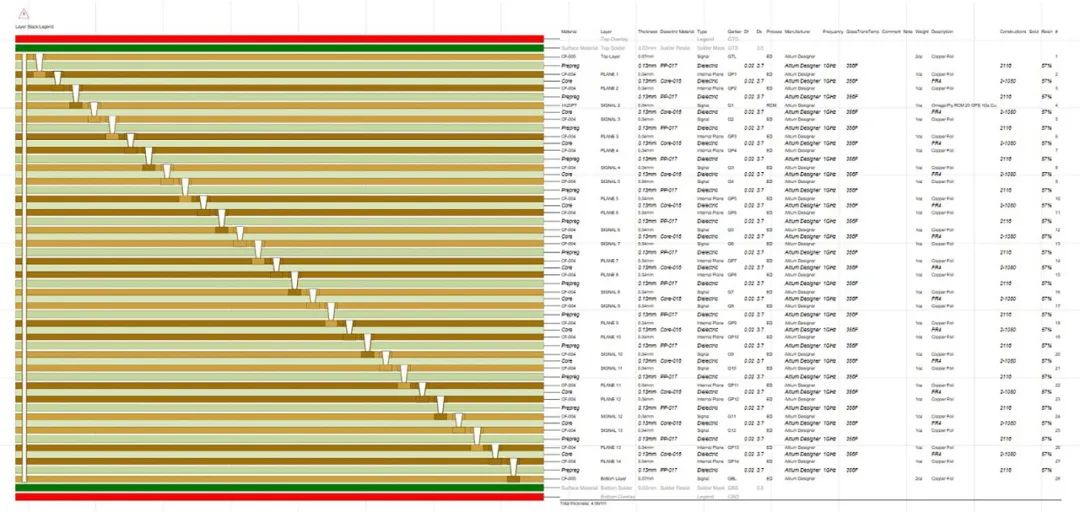

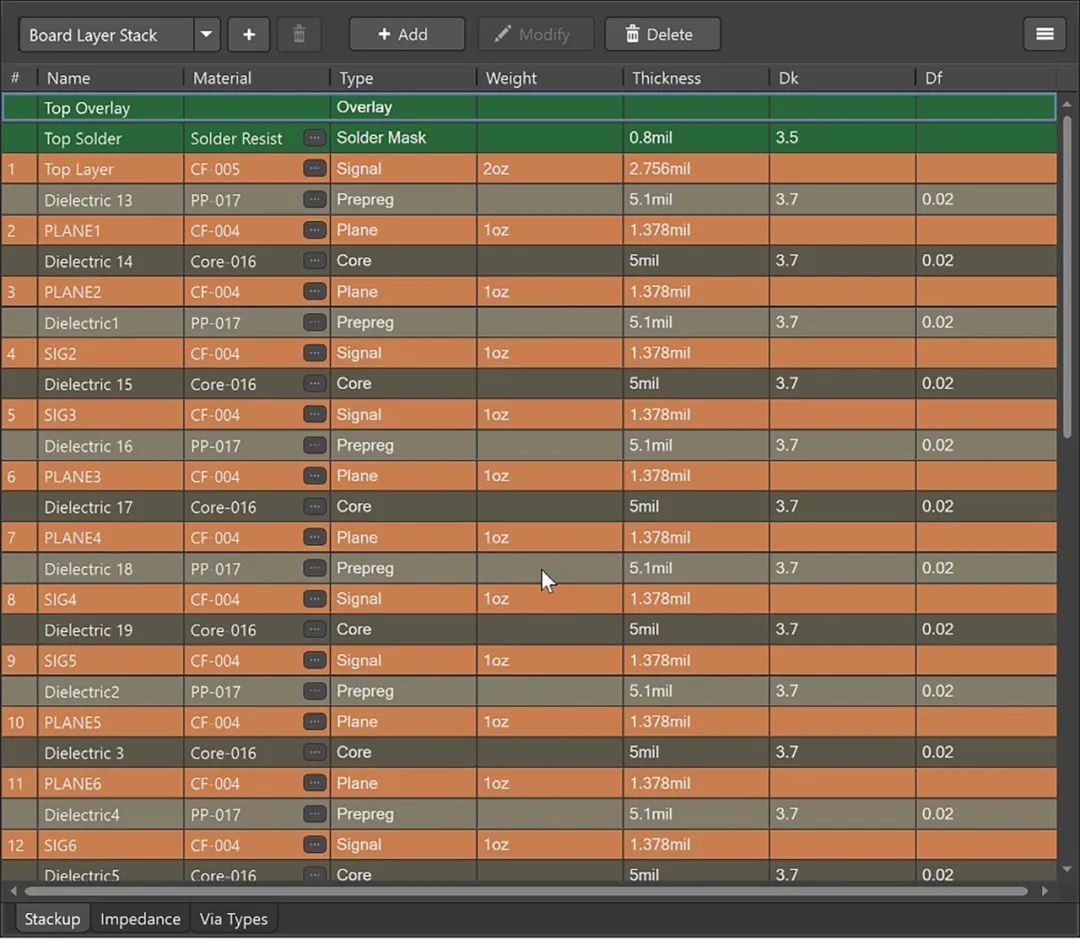

布线BGA的第一个挑战是确定需要多少HDI(顺序层压/微通孔)层。图 2 显示了每一层都是 HDI 层的28 层板结构。但是当前的HDI制造技术无法生产这样的结构。

图 2:每层都是 HDI 层的 28 层板结构,目前的制造工艺无法实现

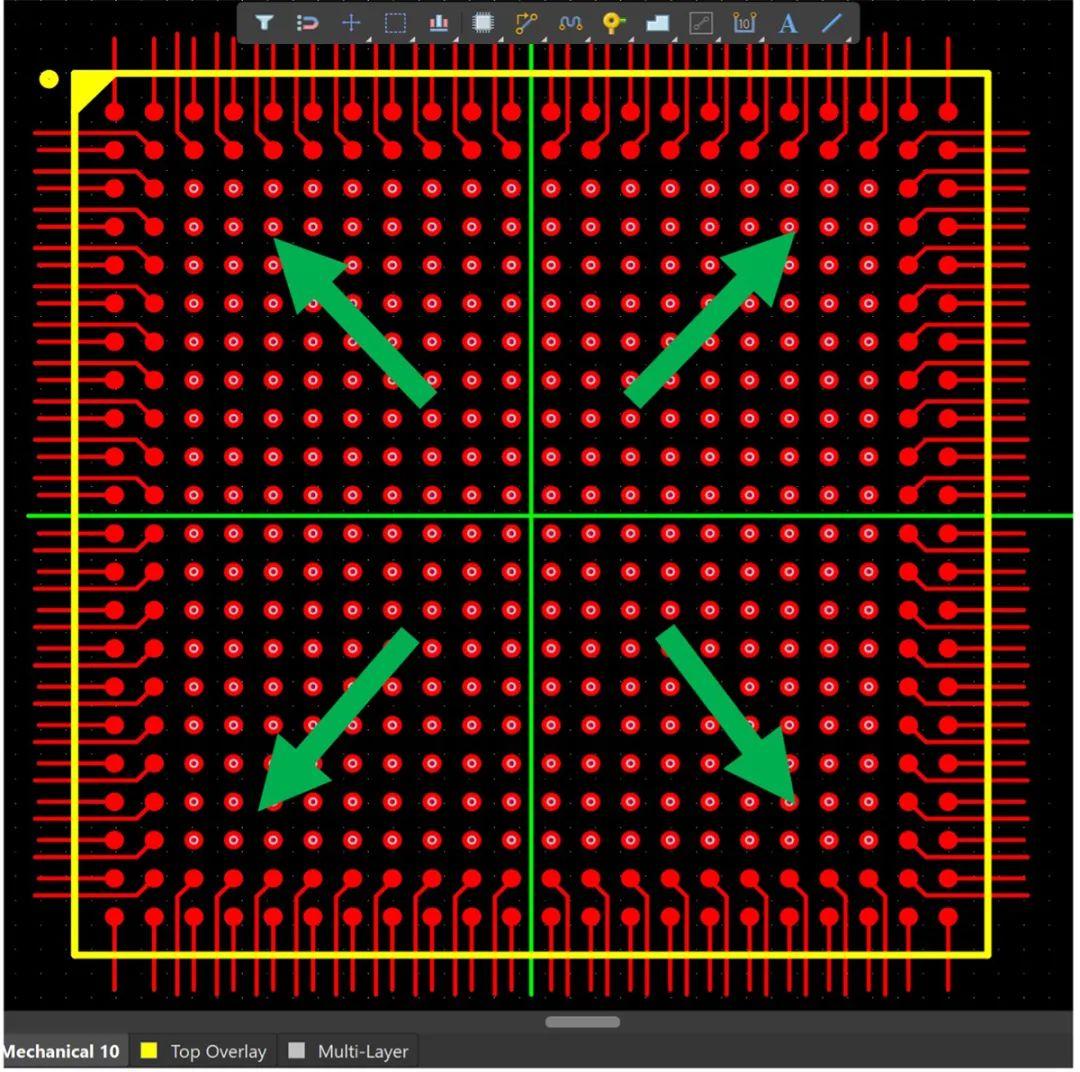

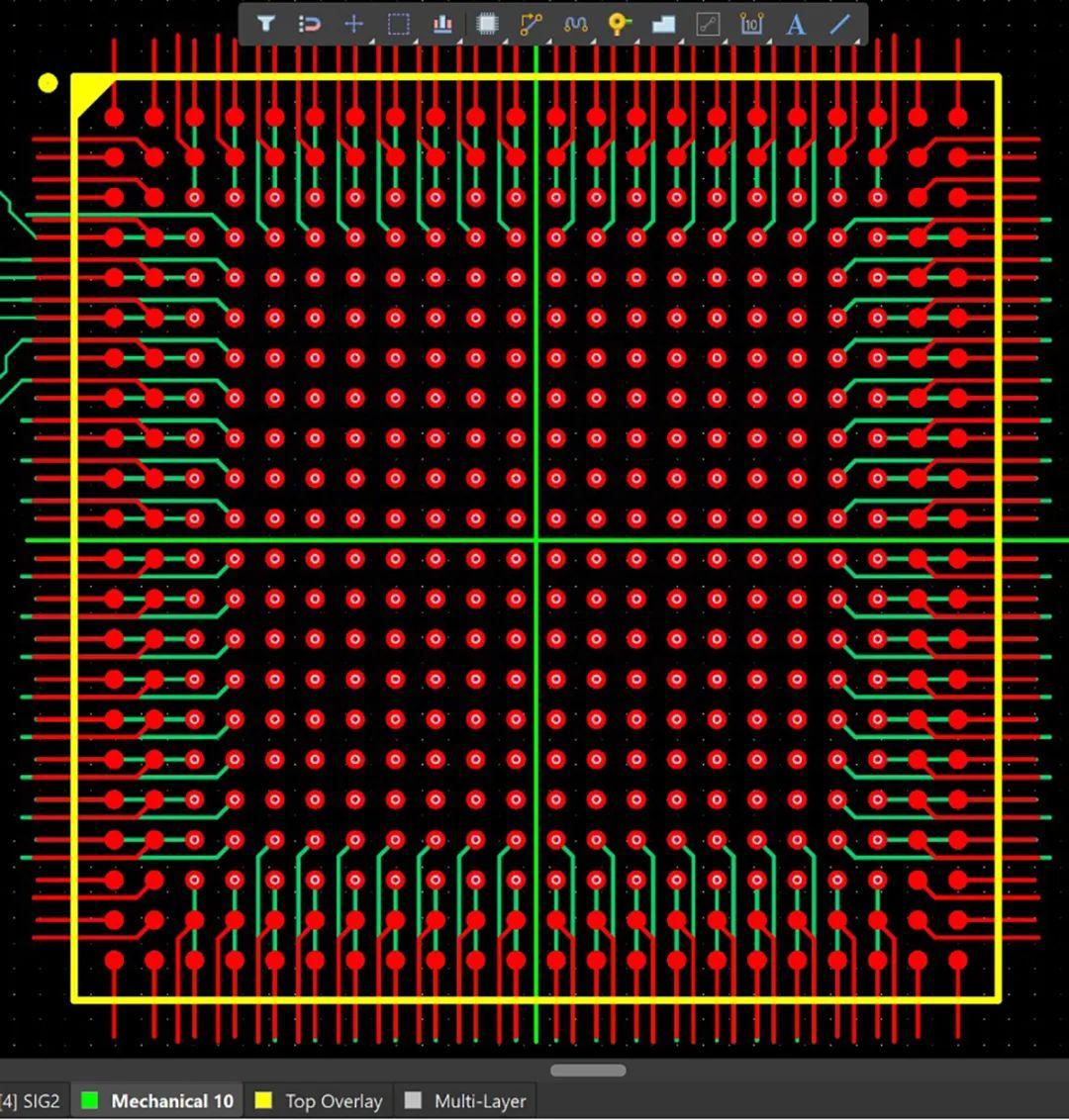

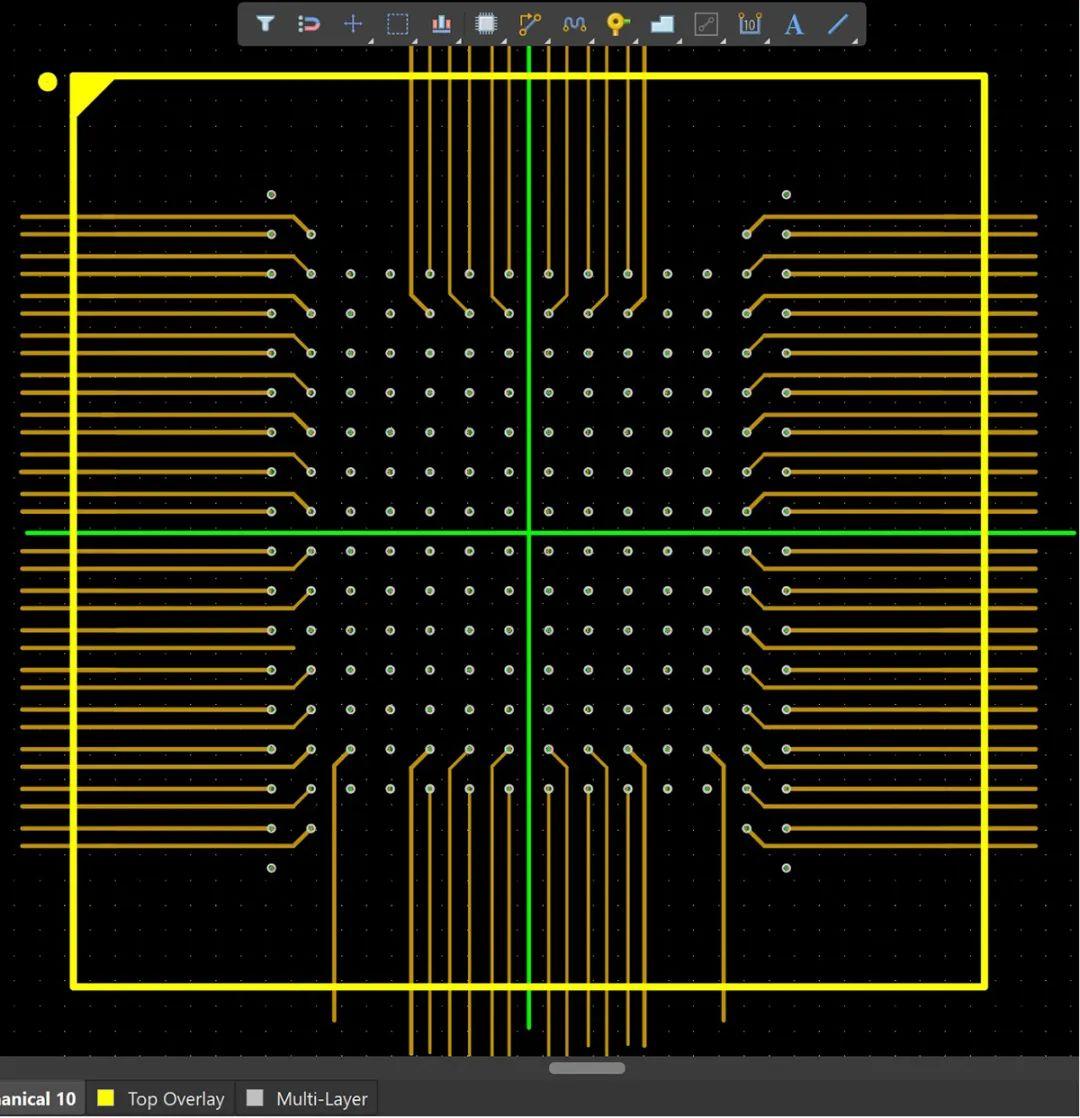

BGA逃逸布线的基本方法是四象限法。通过该方法,我们将BGA划分为4个象限,然后在每个象限中使用标准模式。图3显示了基本象限图形。

图 3:用于逃逸布线BGA的象限图形

界定象限后,将以两行模式布线BGA。最靠外的行可直接布线。靠内的行将沿着象限方向布线,然后直线布线。这里最靠外的两行将在顶层布线。

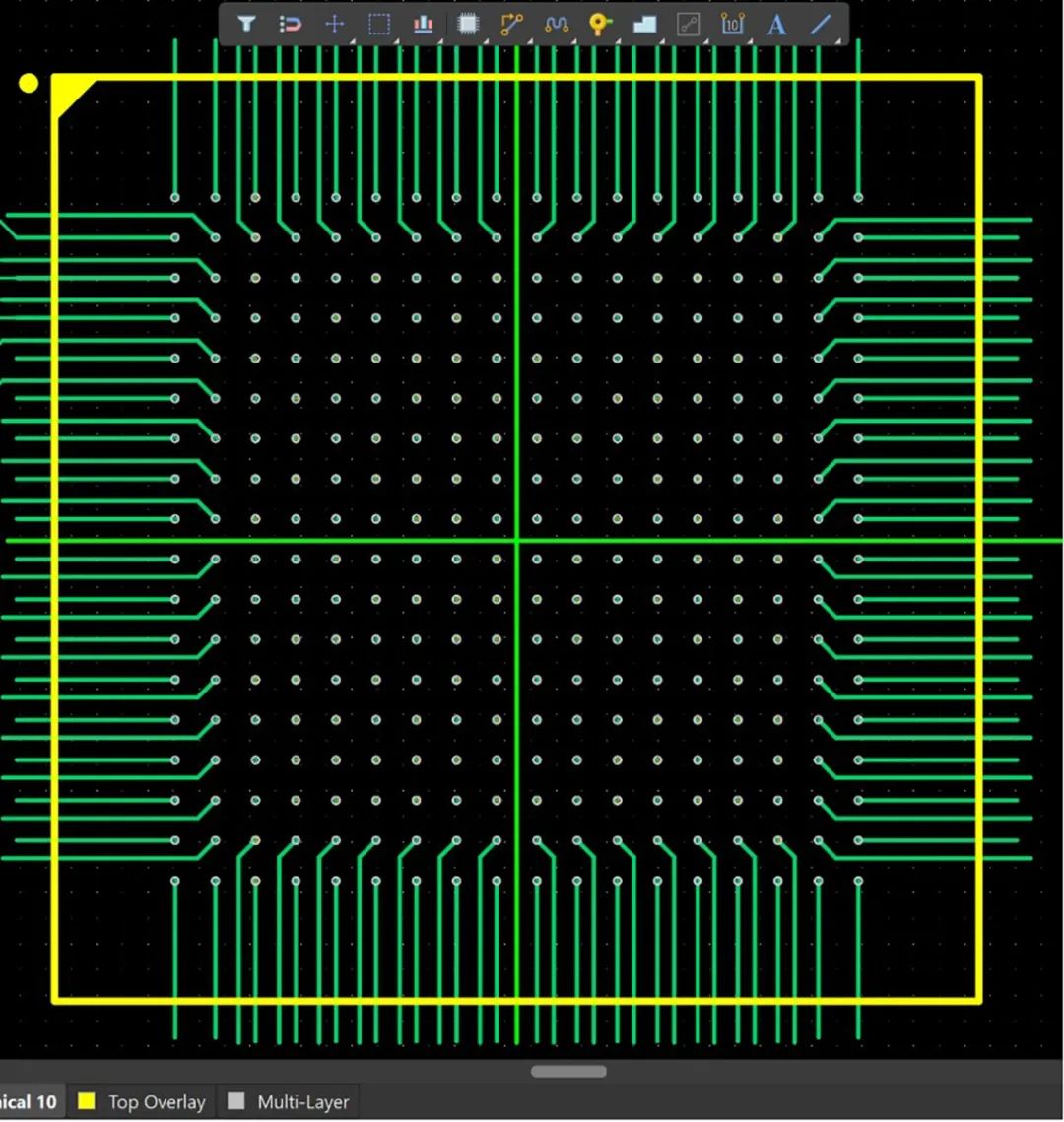

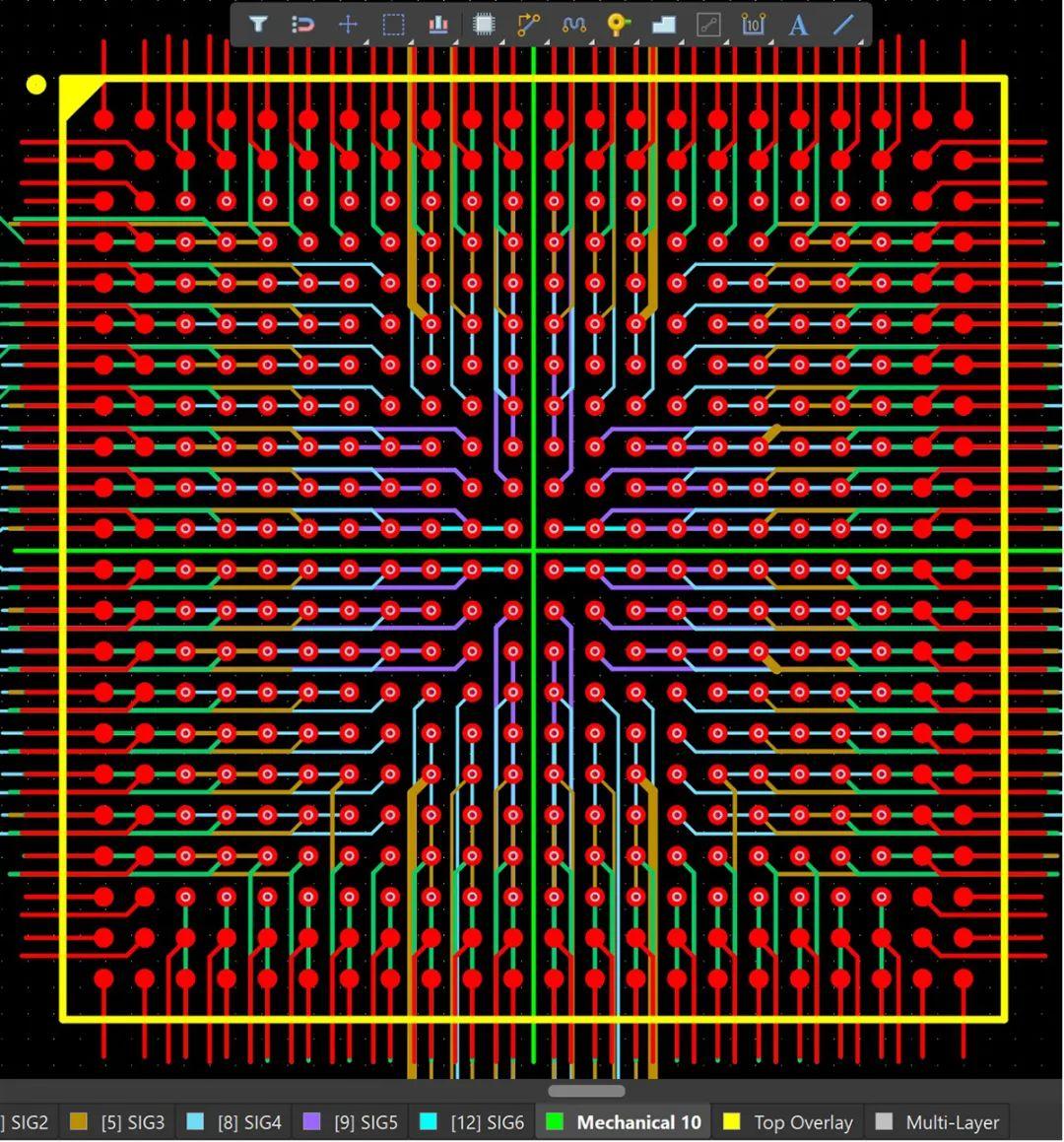

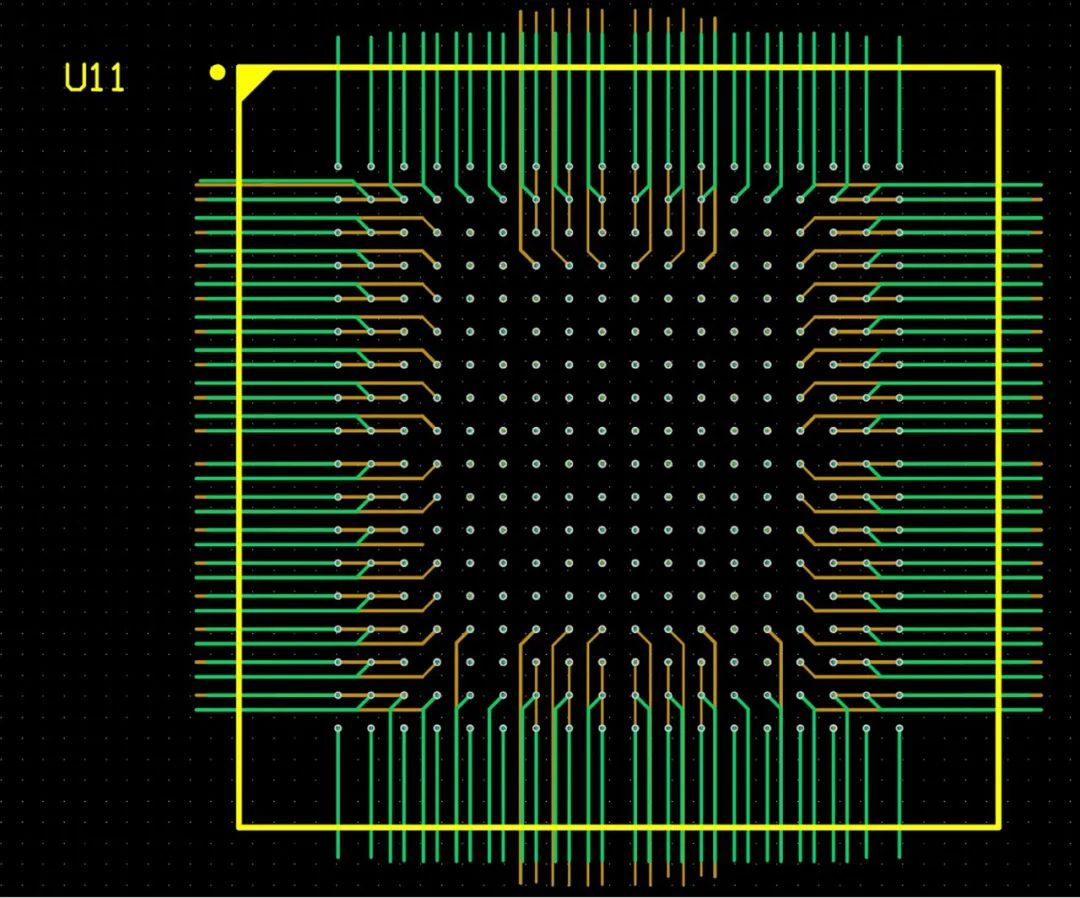

接下来的两行将布线在第一层内部信号层上,依此类推。图 4 和图 5 显示了第一层内部信号层的布线。

图4:第一层内部信号层的布线

图5:第一层内部信号层的布线(续)

图6:该排序的前12层

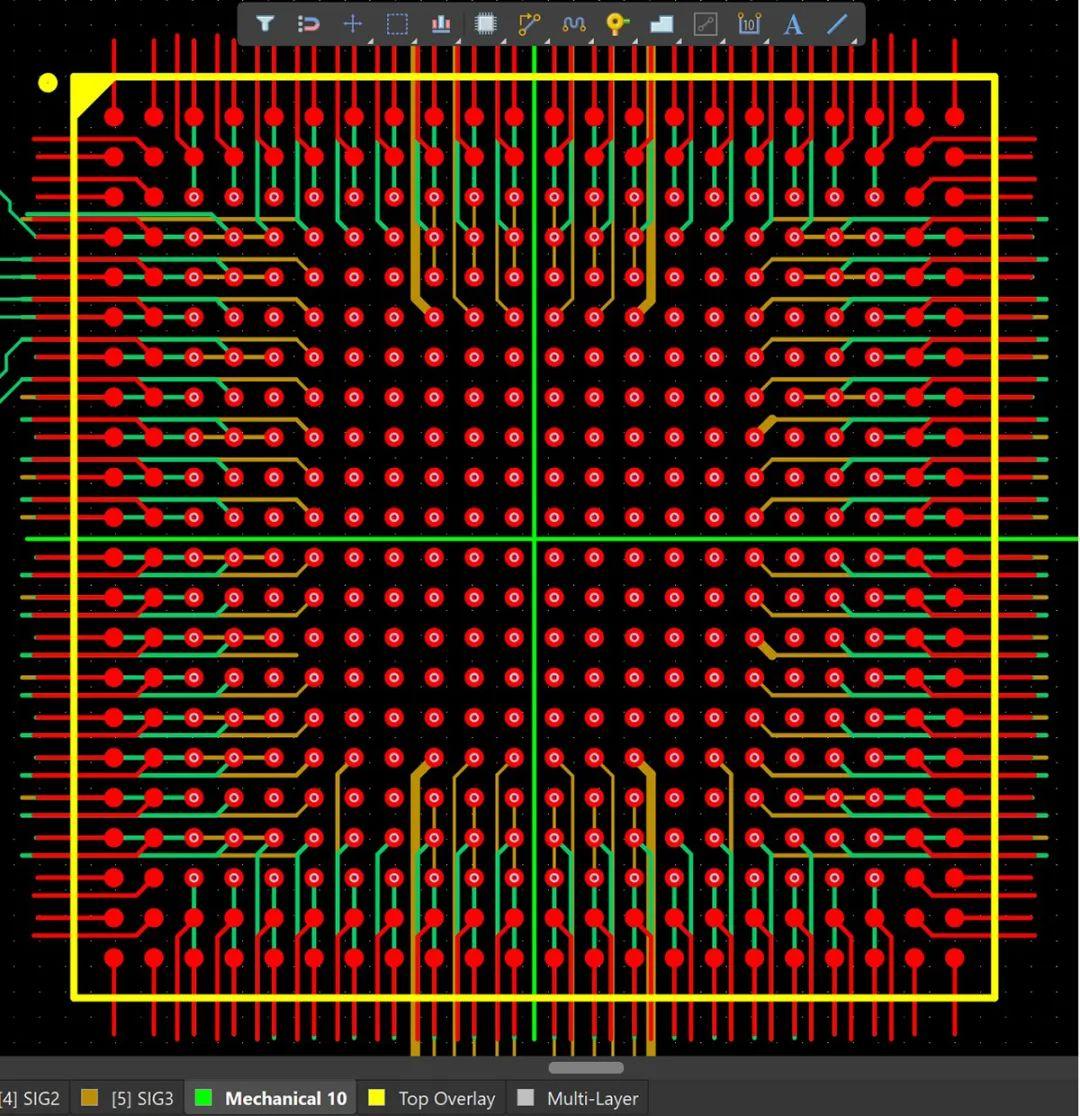

图7:排序中另一个步骤的屏幕截图

图8:逃逸布线顺序(续)

图 9:逃逸布线屏幕截图说明了如今BGA布线的复杂性

图10:两个相邻的信号层——双带状线结构

在这个阶段,从信号完整性的角度来看,应该指出所采用的叠层是适当的(稍后将详细介绍SI)。图6显示了排序的前12层。在该图中,可以看到需要3个微通孔转换来从顶层过渡到第2层信号层,第一层内部信号层,顶层到平面1,平面1到平面2,平面2-第2层信号层。需要平面作为信号层对之间的屏蔽,并且需要平面作为对添加,形成平面电容,以处理数字电路的高速开关电流需求。

关于使用该方法可能遇到的一些信号完整性问题,我们将研究两个相邻的信号层——双带状线结构(图10)。首先,注意同一信号层上走线之间的平行性,以及双带状线的相邻信号层上走线的平行性。对于信号完整性,相邻层上的平行性是更大的问题,因为超过临界长度,可能会导致串扰。

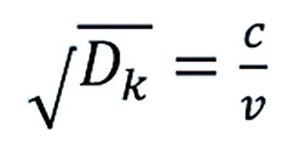

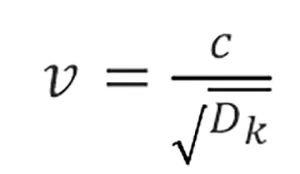

为了这个问题,我们必须了解临界长度是过渡电气长度(Transition Electrical Length,简称TEL)的一半,且TEL是信号在主动驱动期间在传输线(走线)上传播的距离。这就是数字信号的上升/下降时间。为了计算TEL,我们必须用下面的公式确定传输线上的传播速度。

(1)

(1)

其中:

Dk = 介电常数

c = 光速

v = 传播速度

通过一点代数运算,公式1变为:

(2)

(2)

现在假设标准FR-4的Dk为4.0,并使用英制单位(英寸),我们得到以下结果:

c = 983.6 x 106 ft/s

√Dk = √4 = 2

V = (983.6 x 106 ft/s) / 2 = 491.8 x 106 ft/s

(491.8 x 106 ft/s) x (12 in/ft) = 5.901 x 109 in/s

(5.901 x 109 in/s) x (1 x 10-9 ns/s) = 5.901 in/ns

由此可以看出,如果上升时间/下降时间为1ns,TEL约为6英寸,因此半TEL的临界长度约为3英寸。由此可以看出,在需要添加串联端接电阻之前,可以非常容易地逃逸FPGA,而不会出现严重的SI问题。

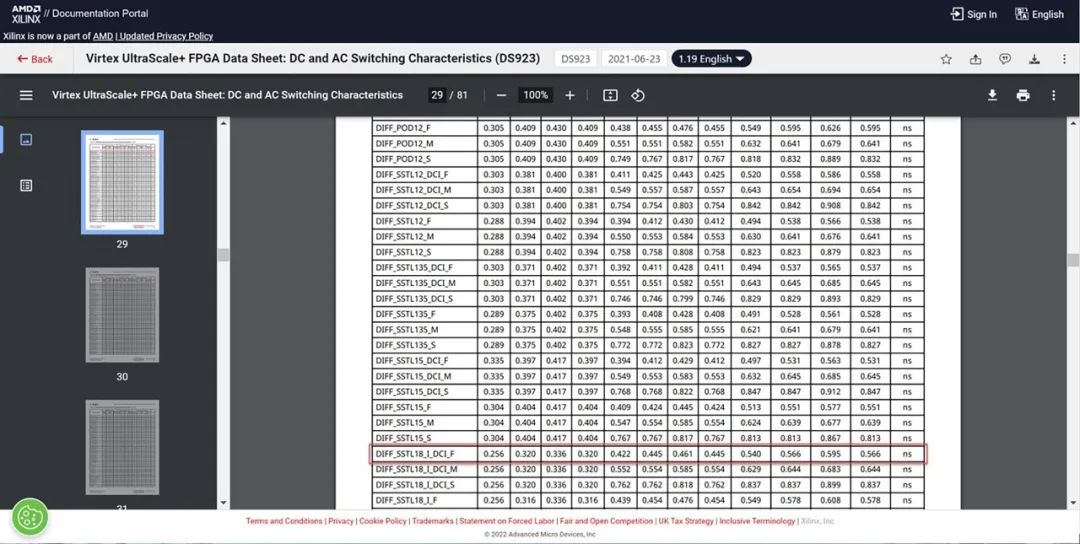

现代FPGA,如16 nm工艺的AMD Xilinx Virtex UltraSCALE+FPGA,切换速度高达0.250 ns(图11)。由此,再次回到公式2,我们得到的TEL为1.475英寸,临界长度为0.738英寸。

图11:现代FPGA的开关速度高达0.250ns

在以个位数纳米通道长度的制程节点制造的下一代设备中,看到上升/下降时间为0.1ns (100 ps)或更快。这为我们提供了约0.6英寸的TEL和0.3英寸或更短的临界长度。由此可以看到,在添加串联端接电阻以获得成功的信号完整性性能之前,不能期望将FPGA走线布线到FPGA主体的外围。

为了成功地解决这个问题,电路板设计者需要在PCB结构中使用成型的嵌入式电阻器。该方法使用PCB结构的特殊层,即在同一层上具有两种不同导电材料。一种是传统的铜,另一种是镍磷(Ni-P)等电阻材料,用于制造与FPGA/BGA焊料球的引脚/通孔一致的电阻器。

工艺节点是指MOSFET的栅极在MOSFET的漏极和源极之间形成的通道长度。图12显示了传统MOSFET结构的示例。随着通道长度变短,电子从漏极移动到源极所需的时间变短(更快);这反过来又导致了现代设备中越来越快的上升时间/下降时间。这也是为什么我们说上升时间/下降时间而不是时钟频率是信号完整性规则必须应用于设计的决定因素。

关于如何从现代FPGAs中逃逸布线的问题,为信号完整性所需的串联端接集成了埋入电阻之后,仍然存在相邻层上平行走线的串扰。使用的主要方法是z轴的走线分离。

如果无法在相邻层的走线之间获得足够的间隔/偏移量,则需要添加额外的平面层,以在走线层之间提供屏蔽/隔离。这种方法有其自身的问题,因为需要向电路板添加许多层,这会由于增加的层数而增加质量和整个制造复杂度,以及信号完整性需要始终添加平面作为Vcc/RTN的对,以为实现信号完整性增加平面电容,为实现可制造性提供适当Z轴铜平衡。

正如我们所看到的,随着封装尺寸的减小和器件速度的提高,逃逸布线FPGA/BGA将持续给现代PCB设计师带来重大挑战。

参考内容

“Simulation study of scaling design, performance characterization, statistical variability and reliability of decananometer MOSFETs,” PhD thesis by Xingsheng Wang at University of Glasgow, May 2010.

Kris Moyer具有互连设计师/高级互连设计师资格,是IPC设计讲师,任IPC 1-13委员会主席。

欢迎扫码关注我们的微信公众号

“PCB007中文线上杂志”

点击这里即可获取完整杂志内容。