诸多因素汇集,推动了小芯片设计的革命。首先是硅片小型化带来的经济优势正在减弱。

半导体行业正面临着一个拐点;由于成本增加、良率下降以及掩膜尺寸限制,促使需要能够替代已达到物理极限的传统单片解决方案的可行方案。许多拐点问题都来源于以下原因:将芯片制程缩小到 10 纳米以下所实现的性能和功耗优势在减少,以及最先进的节点上与物理相关的问题越来越多,比如多种类型的噪音、热效应和电 迁移。

这推动了一种新兴趋势,即将通常意义上的片上系统 (SoC) 分解为固态的制造完成的 IP 模块或小芯片,它们通常只包含几项功能,从而实现多芯片异构集成。

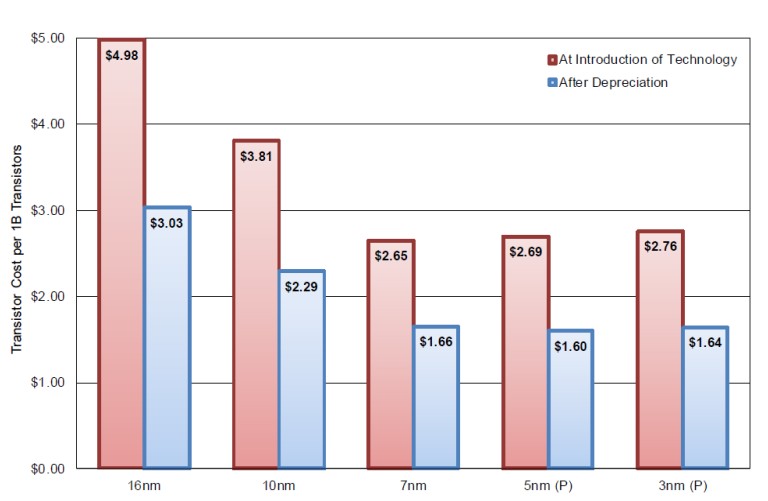

图1: 不同制程技术的晶体管成本。(信息来源:International Business Strategies 2020)

点击这里,下载完整白皮书

来源:Mentor

标签:

#Design

#产品设计

#Mentor

#技术

#白皮书

#下载

#异构小芯片

#设计

#集成