大约在25年前,我还是高速PCB设计领域初出茅庐的一名新人,当时接触到的产品运行速度慢、PCB层数少、介电常数和损耗因数高、设计裕度较大、铜粗糙程度不重要、玻璃纤维布的编织方式也不重要。当时的介质为“FR-4”,其属性也不太重要。快速PCI总线的运行频率只有66MHz。

20世纪90年代开始,PCB的运行速度逐步加快,PCB制造商购买了软件工具来设计叠层,以达到目标阻抗。在此过程中,他们会购买PCB层压板数据库,在设计流程后期(通常在初次信号完整性仿真和分析后的几周或几个月)将涉及的叠层提供给OEM客户,包括材料厚度、铜厚、介电常数和走线宽度。

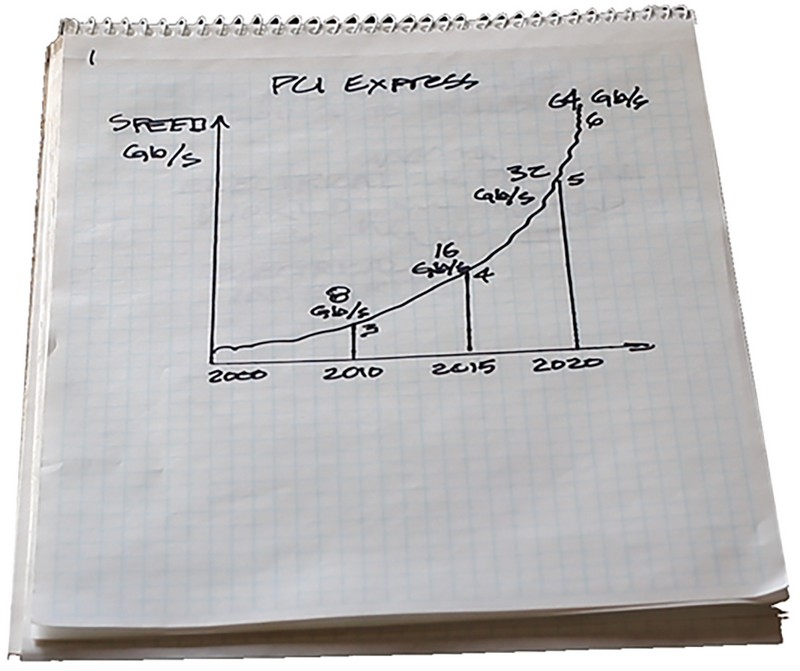

进入21世纪,PCB的运行速度持续升级,设计余量持续收紧,OEM工程师开始以毫伏(mV)和皮秒(ps)为单位跟踪信号。图1展示了2000年开始的运行速度趋势,强调了PCI Express的发展路径,从2010年的PCIe 3.0到PCIe 6.0,而PCIe 6.0也只是入门级。

图1 :从2000 年开始,互连速度以为每秒千兆位(Gigabit Per Second,简称Gbps)为单位

在网络研讨会和培训会上我经常问“为什么要做模拟测试?” 的问题,之所以这么问是因为这个问题的答案能帮助我了解听众。很久之前,某位智慧的长者曾告诉过我和我的学生,要“了解听众的水平”。

每次问这个问题时,得到的答案都是诸如信号速度更快、计算阻抗或损耗、避免符号间干扰、控制串扰等。这些都是不错的答案,但在我看来还是没有说到关键点上。

某位机智的信号完整性专业人士曾说过,进行模拟测试只为两个理由:

- 做出设计相关决策(即在设计过程中权衡利弊、做出取舍);

- 在进入制造阶段之前验证设计(验证环节)。

设计师唯一在乎的问题就是“设计能否正常运行?成本是多少?”也就意味着仿真应该能够生成关乎设计成功与失败的实际指标。这样很合理。

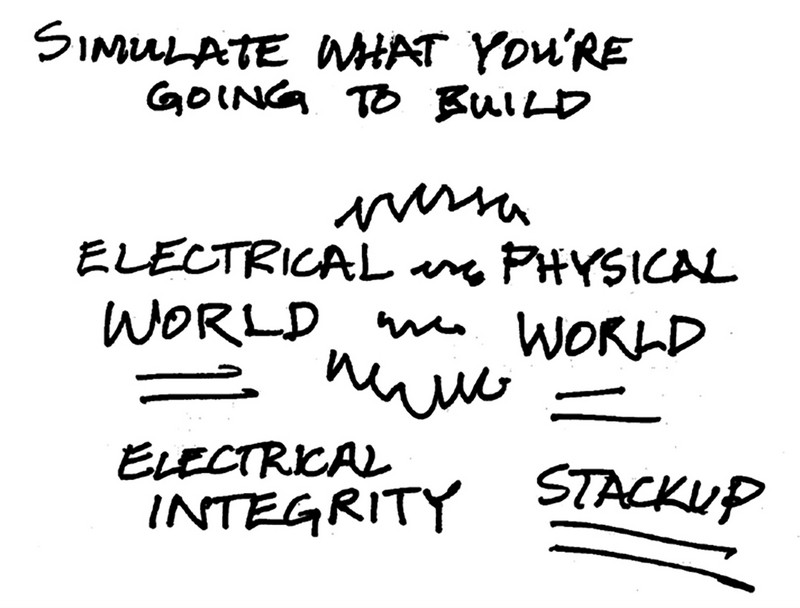

上述内容很好地描述了“为什么要进行模拟测试”,但到目前为止,我还没听到任何人谈到最根本的原因。在我看来,信号完整性模拟(SI)或电源完整性模拟(PI)的目的是:预测物理界对电气界产生的负面影响,并减缓或积极预防负面影响的产生。

你也许拥有价值几十万美元的VNA、示波器和仿真软件,但除非你在建模过程中仔细考虑所有PCB制造的细节,否则仿真操作将是无效的。连接多个制造商的高速设计之间的桥梁会穿过PCB的主干 ——叠层,它会接触到每一个高速信号。我在图2中给出了展示。

图2 :进行信号完整性仿真或电源完整性仿真最根本的原因就是预测物理界对电气界的负面影响,并减缓或积极预防负面影响的产生

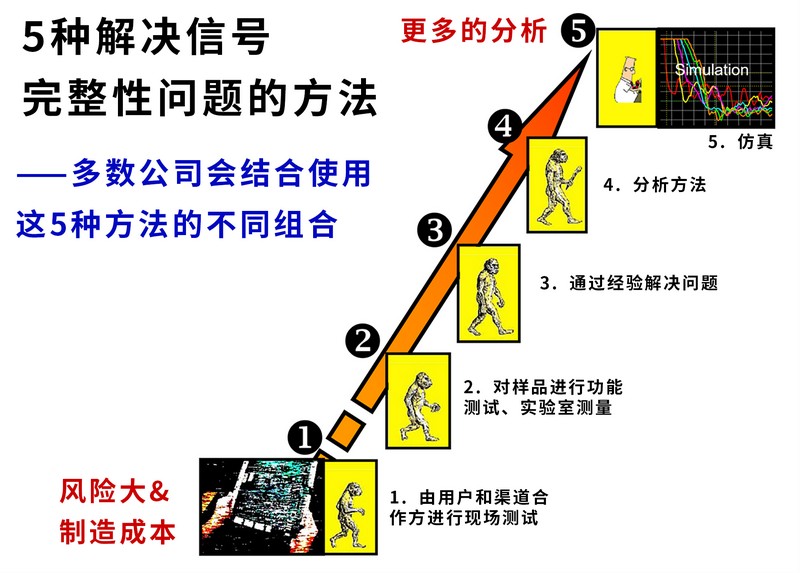

仿真的发展演化

如图3所示,多年来模拟硬件性能的发展共有5个不同阶段。

图3 :多数公司会结合使用这5 种方法的不同组合来解决信号完整性问题。

为此,我需要像图2中展示的那样,尽最大努力来“模拟要构建的产品”。好的模拟器可以加快模拟速度,留出足够的时间对替代方案进行模拟测试,使工程师不仅可以优化信号质量,还可以优化成本。

但拥有昂贵的仿真工具远远不够。在工作中我会经手很多PCB叠层,设计中涉及到的人员和工具有所不同,所以针对阻抗和信号损耗产生影响的制造参数也是设计团队可以研究的对象。在逐渐加速过程中,信号完整性的关键因素目前不仅包含阻抗,还包括损耗、铜粗糙度和玻璃纤维布编织的角度。确实,在真正构建PCB叠层的过程中发生的一切都会对信号质量产生负面影响,不仅PCB叠层的细节要纳入考量范围,还要考虑到参与设计的每家PCB制造商的叠层细节。

影响阻抗的因素

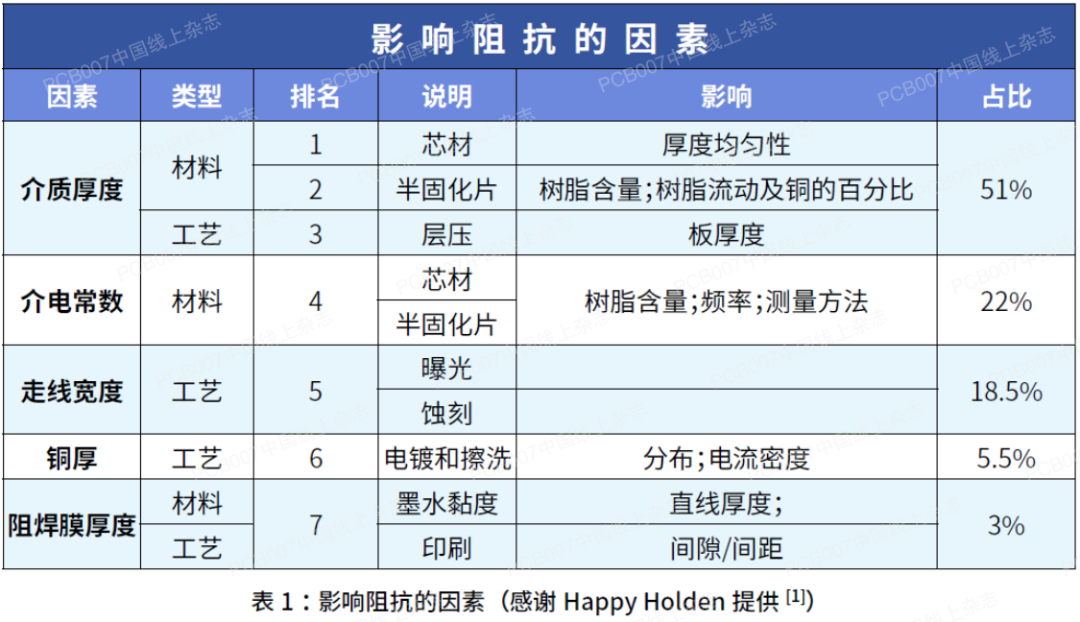

EDA工具(包括我们公司生产的在内)用途很广,前提是要了解真正建模的对象是什么。即使是这样,结果完全依赖于输入的数据,仿真水平由输入的数据决定。表1所示是影响阻抗的主要参数,包括各自的影响程度。

从上至下查看此表,会对电介质厚度有更好的把控,会了解如何给额定参数留出足够余量,让产品在制造过程中不会出现问题。但我发现工程设计团队还是把重心都放在了分析数据上,但这些数据中的指标存在问题,而且他们也没有完全领会上表提到的参数及其优先项(从1到7)。

例如,我从没见过哪个PCB制造商用实际PCB布局中选取的每层铜占比的数值来计算压合后的半固化片厚度。表1中第4个数据的问题尤其严重。我在硬件OEM、PCB制造商和层压板制造商中做过深度调查,得出的结论是PCB工艺中人们了解最少的参数就是介电常数。走线宽度(#5)和制造商蚀刻工艺密切相关。研究表明,一般PCB供应商对半盎司铜凹蚀保持约为0.25mil,对1盎司铜凹蚀保持约为0.5mil。高级PCB制造商则可分别做到0.17mil凹蚀(半盎司铜)和0.45 mil凹蚀(1盎司铜)。如果能了解制造商的水平并在仿真过程中建立相应模型,就能使阻抗的精度再精确几欧姆。

铜厚(#6)是另一个会影响阻抗的参数。我经常看到工程师、设计师和EDA工具上把半盎司铜的额定厚度上调凑整为0.7mils(18μm)、1.4mils(36μm)和2.8mils(71 μm)。通常情况下我不反对凑整,但上调凑整还是下调凑整是要视情况而定。表2列出了实际多层PCB中常用的铜厚度和单位转换,其中包括IPC-4562A规定的标称厚度。

PCB厚度也会受到影响。4层板设计可能不会受到太大影响,但如果是铜重达到1盎司的20层PCB用了错误凑整的数值,整个厚度的误差就会多达4mil。如果PCB设计师能用更精细的数值设计产品,我猜机械工程师会非常感谢他们的。

总结

每次和SI顾问聊天的时候,我都会问他们一个问题 :“你接手的有关严重SI问题的紧急项目中,有多少会出现与叠层相关的问题?”

到目前为止,我得到的回答都是“100%”。我提到的那些会影响阻抗的因素会使设计处于容差目标的边缘。所以说仅仅购买一台昂贵的模拟器是不够的,还要输入恰当的参数值,这也是Z-zero公司过去几年里的工作重心。如果你有相关的故事愿意分享,欢迎发邮件联系我。 我非常喜欢听最前线的设计师分享他们的故事。

Bill Hargin 是资深信号完整性工程师,Z-zero 公司创始人。

更多内容可点击这里查看,文章发表于《PCB007中国线上杂志》6月号,更多精彩原创内容,欢迎关注“PCB007中文线上杂志”公众号。