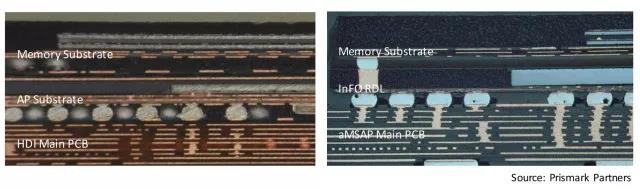

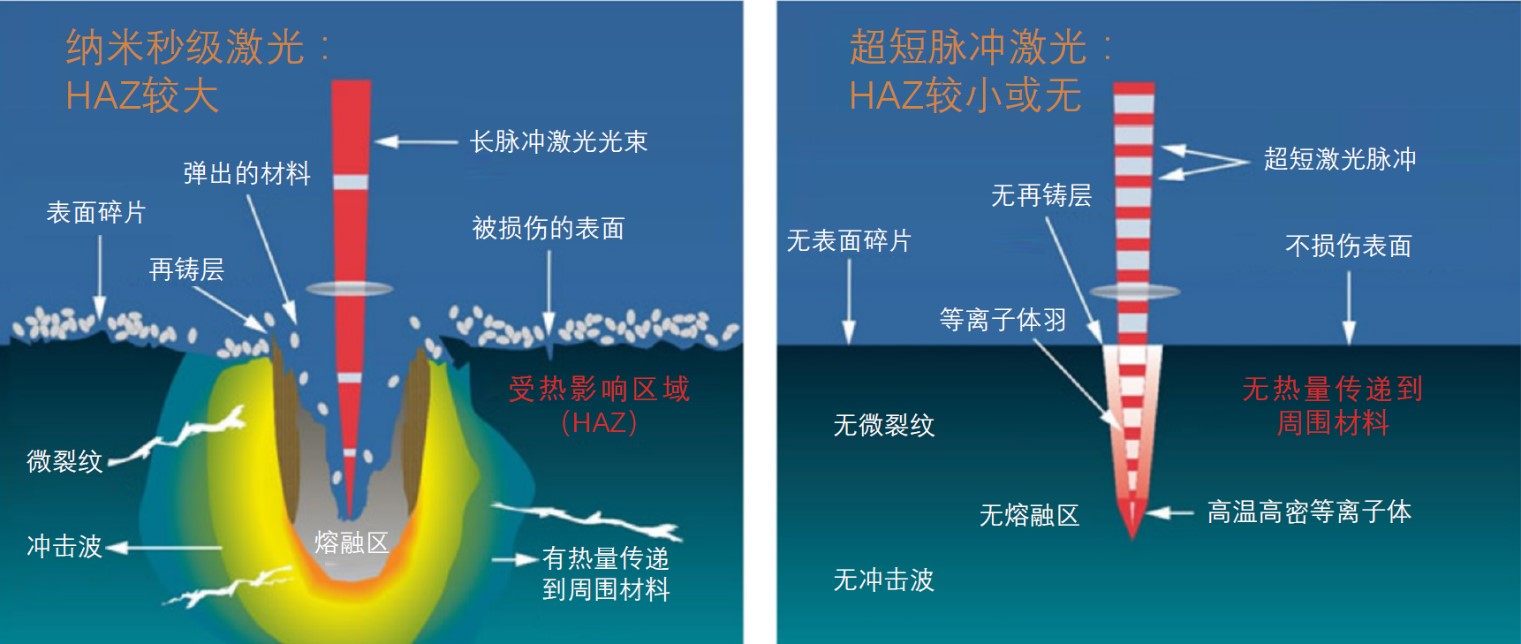

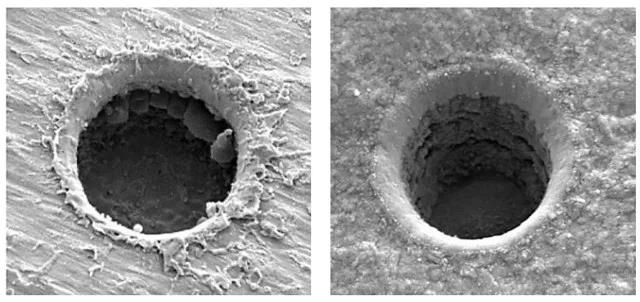

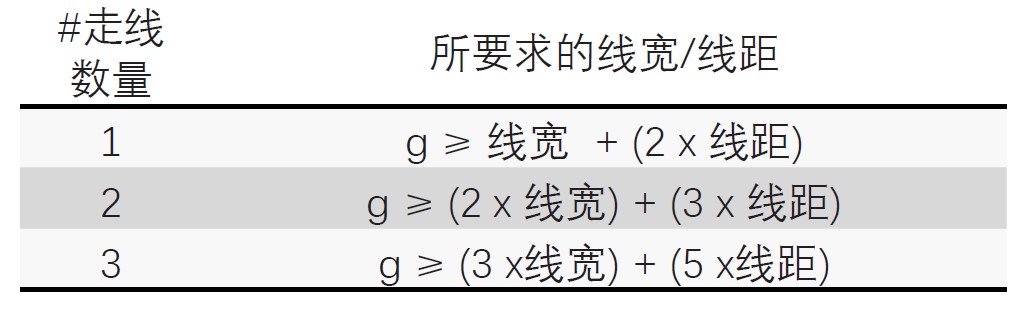

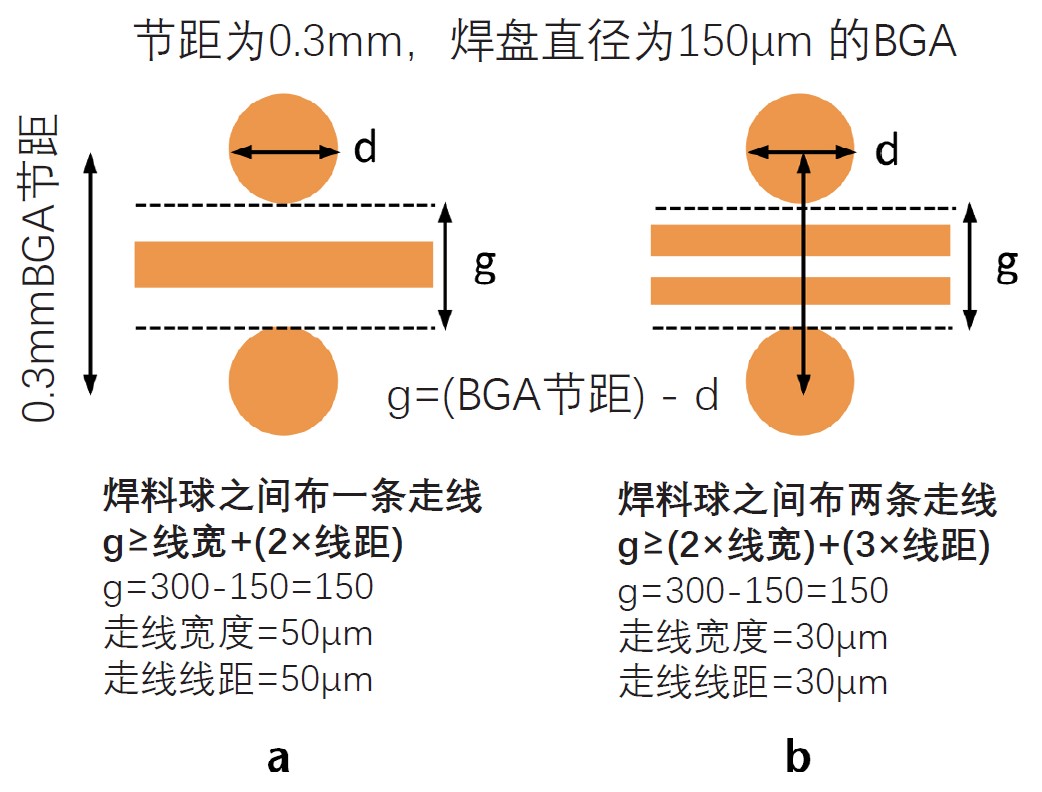

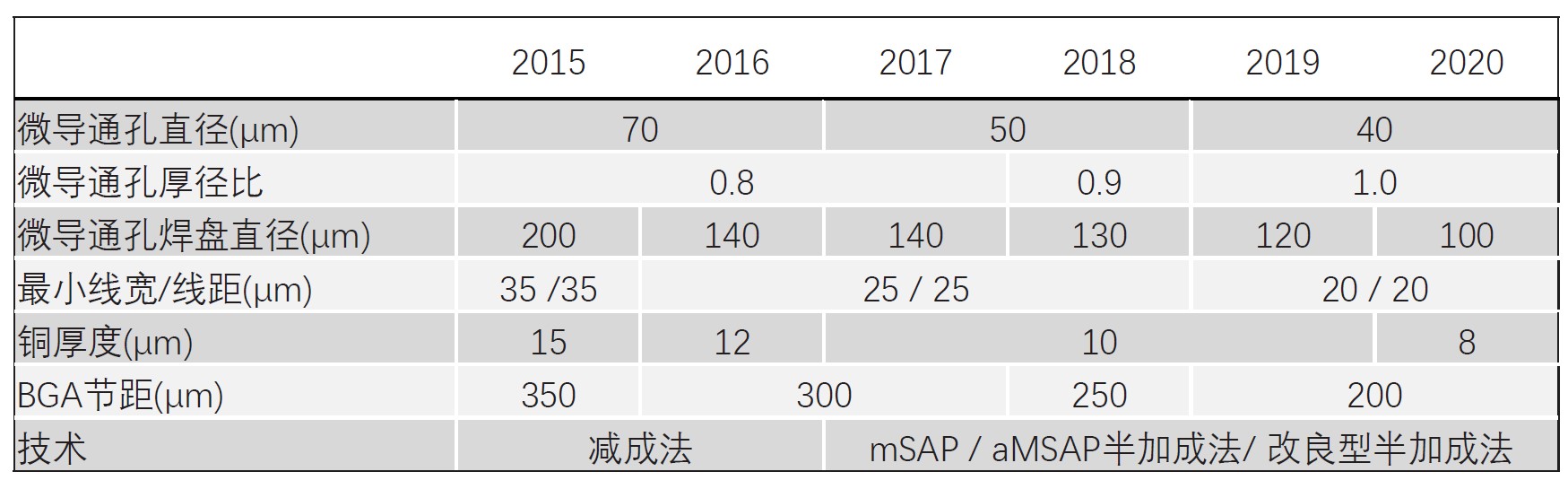

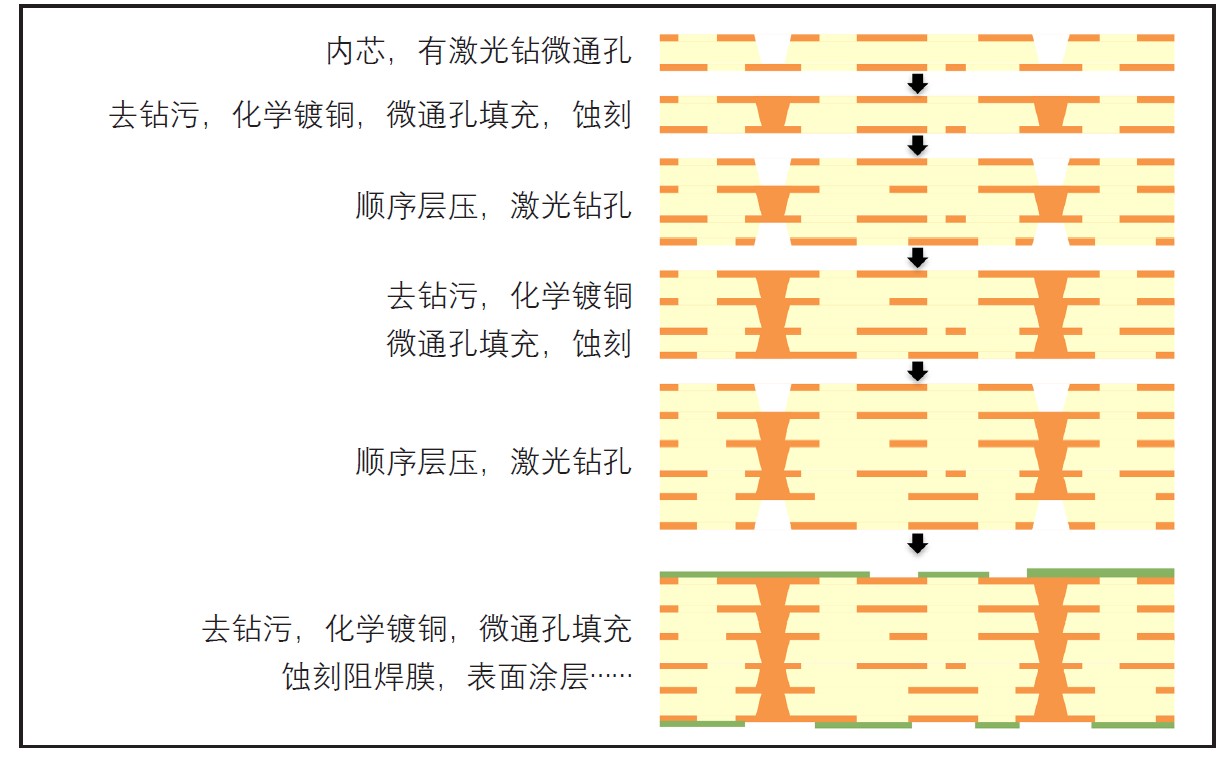

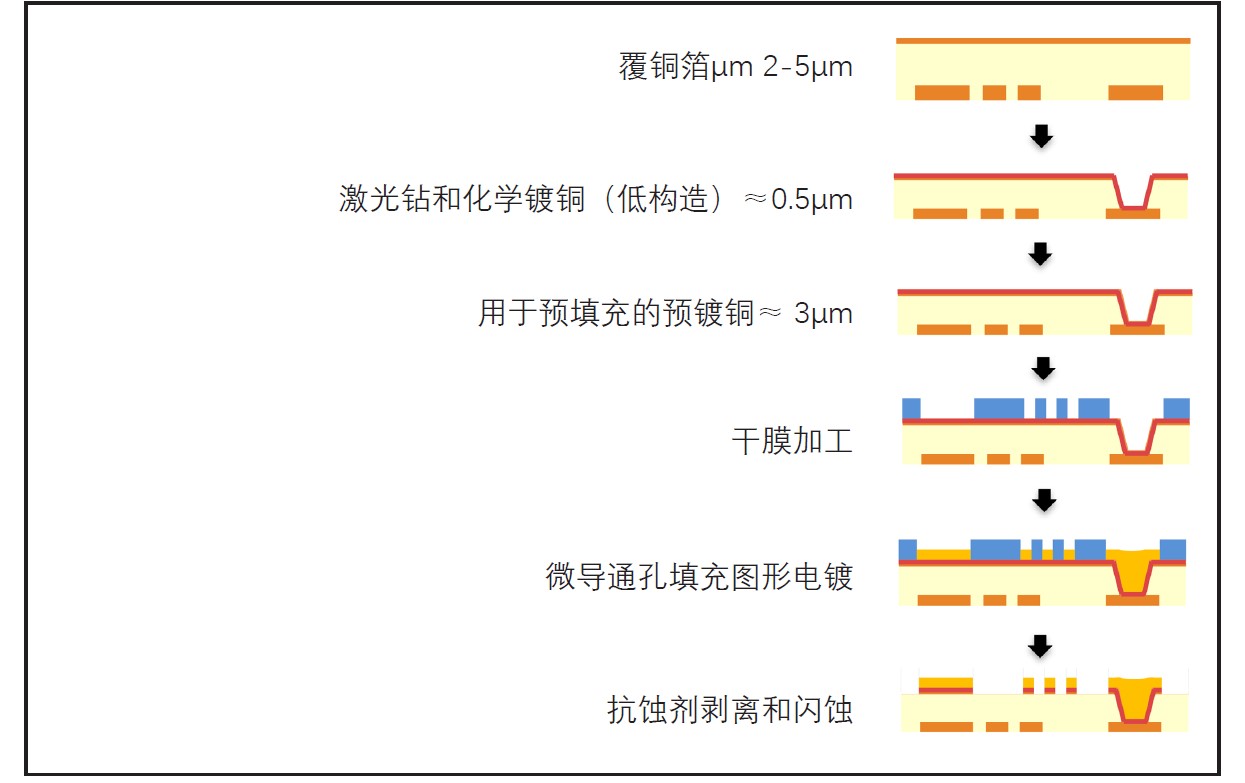

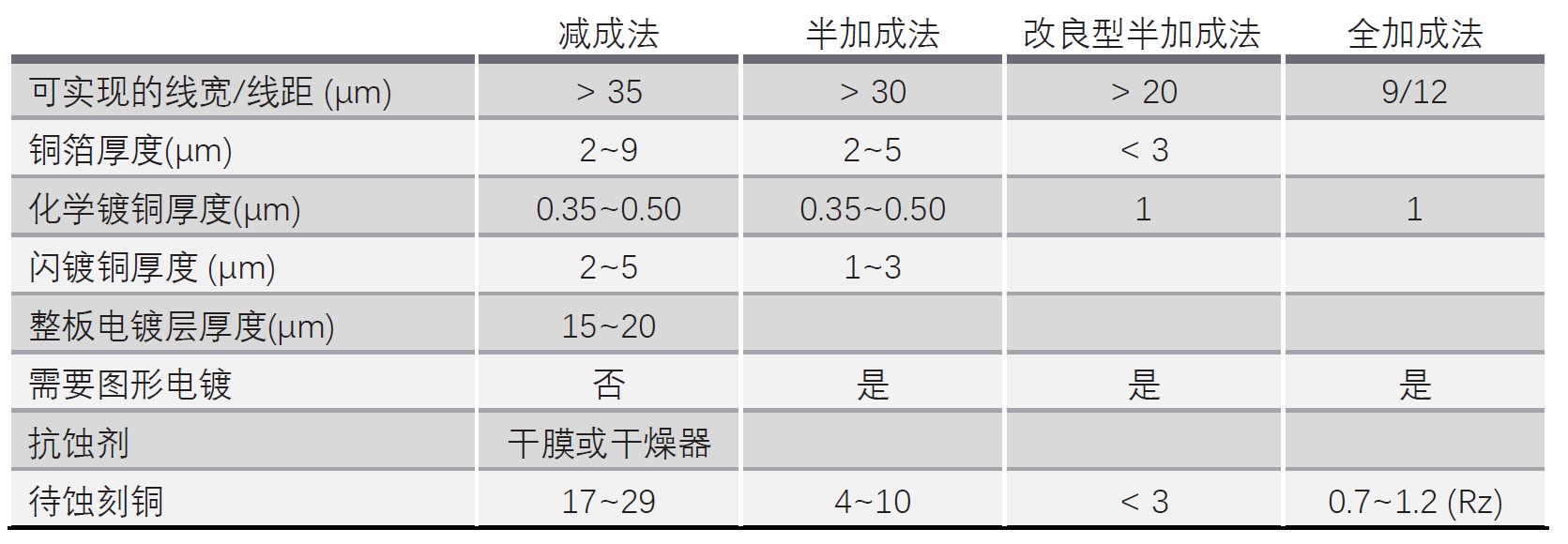

HDI PCB的发展 自20世纪90年代早期到中期以来,HDI PCB经历了几次变化,现在可以说是进入了第三个发展期。 早期的HDI板基于减成法或印刷蚀刻工艺,利用传统的板芯和顺序层压步骤可生产线宽/线距约为60μm的高端电路板。最重要的是,依靠微通孔来达到当时用其他技术很难实现的高密度互连特性。 随着PCB制造商不断改进工艺,HDI电路板性能也得到了改善;随着智能手机的发展,21世纪初,第二代HDI应运而生。在保留激光钻微通孔的同时,堆叠的通孔开始取代交错的导通孔,并结合“任意层”构建技术,HDI板最终的线宽/线距达到了40μm。 这种任意层的方法仍然基于减成法工艺,而且可以肯定的是,对于移动电子产品来说,大多数高端HDI仍然采用这种技术。然而,在2017年,HDI开始迈入新的发展阶段,开始从减成法工艺转向基于图形电镀的工艺。 半加成法(SAP)采用图形电镀工艺,可使电路特征<15μm,主要为应对封装载板尺寸要求。 然而,半加成法(mSAP)和改良型半加成法(amSAP)是经过修改和高级修改后的版本,现在有望成为下一代HDI PCB主要采用的工艺。 市场发展趋势及驱动力 手机设计 图1:智能手机的演变(资料来源:iFixit、TechInsights、Teardown.com、IHS、Prismark Partners) 通过图1,我们观察到手机的发展演变,表现出有趣的结果: · 手机厚度逐渐下降,目前为7~8毫米 · 手机面积增加,目前通常为90 cm2 ~100 cm2 · 电池尺寸通常随整体手机尺寸成比例增加 · 主PCB面积从约25 cm2下降到15 cm2~20 cm2 · PCB层数一直保持不变,约为 10层 · PCB复杂性增加,线宽/线距从60μm降至约 30μm 因此,为了实现现代手机设计,同时为所有装入手机的其他部分留出足够的空间,HDI必须变得更薄、更小、更复杂! 芯片封装 PCB厚度和面积需求的变化归因于手机的结构设计,这无疑会增加PCB的复杂性,但大部分额外的复杂性要追溯到芯片封装的需求。而且,由于许多元器件现在被封装在一些面阵列形式中,所以我们需要考虑焊料球的数量、直径和节距。 简单来说,芯片比以前更加复杂,不管芯片是否封装,这通常意味着它们具有比过去更多的I/O。为了推动I/O数的增加,并且仍然最小化封装占用面积,一个总的发展趋势是减小焊料球直径和焊料球之间的节距。与此同时,I/O数的增加也意味着需要更多的布线来扇出那些I/O,通常可以通过更细的走线来实现,前提是遵循以上概述的面积和层数限制。 图1显示了最近的手机设计对最小线宽/线距的要求从前几代的50μm降至了目前的30μm。采用全减成法PCB工艺无法达到这一要求,因为蚀刻期间出现的问题是不可接受的,因此需要采用加成法工艺的一种变体,而这种工艺反过来又需要对PCB生产工艺进行全面审查。 缩小线宽/线距的最新驱动力与2016年iPhone 7的发布有关。由于iPhone 7,Apple选择放弃基于应用处理器(AP)封装的载板,选择台积电新的InFO(集成扇出)封装。 对于InFO,典型的IC载板被直接沉积在芯片和封装模具表面上的精细特征再分布层(RDL)取代。这些封装类型集中分组为扇出晶圆级封装(FO-WLP),不仅可以减小厚度,还可以在RDL中应用低于5μm的线宽/线距,从而显著增加I/O数量,并且随着焊盘节距的减小,可以在不增加占用面积的前提下实现。更重要的是,所有这些都是在最大化电气和热性能的同时实现的,这在现代智能手机设计中显得至关重要。 图2:基于载板的AP封装(左);使用台积电InFO的无载板AP封装(右) (来源:左图为Prismark Partners;右图为Atotech) PCB技术发展趋势 除了封装,PCB生产还有许多其他发展趋势,所有这些都关乎制造的关键工艺,并将影响HDI设计的发展。 使用已建立的成套工具,今天大多数的微通孔都是由二氧化碳激光器形成的。 该工艺的一个缺点是会在载板内产生大量的热量,这将导致在每个钻孔位置形成热影响区(HAZ),因此会影响最小导通孔节距、尺寸,以及质量。 图3:激光脉冲持续时间对HAZ的影响 (来源:IPG Photonics) 为了解决这个问题,激光器制造商正在开发具有超短脉冲(USP)激光器的新工具,该工具用皮秒或飞秒脉冲代替现有的纳秒脉冲。 这种激光系统可以形成更小的导通孔,同时更小的HAZ产生,这意味着可以大大减小微通孔节距,并且随着激光吸收的改善,导通孔获得更好的质量,具有更少的表面碎片或“飞溅”。 随着这些激光系统的出现,微通孔密度的性能将提升至另一高度,从而实现HDI性能的大幅提升。 图4:用纳秒激光(l)和USP激光(r)形成的典型微通孔(来源:Orbotech) 形成微通孔后,下一个问题就是电镀。虽然导通孔没有显著的厚径比变化,通常保持在0.7~0.8,但它们的尺寸不断减小,这对电镀来说是一种挑战。一个重要的发展是能够用铜完全填充导通孔,这使得导通孔能够直接相互堆叠。这一点影响很大,堆叠导通孔是HDI设计的组成部分,因为它们可以节省空间,特别是与交错导通孔相比,改进了热和电气管理,其上佳的表面平整度也有助于最终的组装良率。 最近的一项电镀新进展是通孔填充(THF)工艺的发布。实芯铜柱将改善热关键区域的导热性,从而改善冷却效果,并且因为仍然可能使用焊盘内导通孔,THF还可支持增加的I/O密度。 图5:堆叠的导通孔和通孔填充 BGA设计规则 在许多情况下,项目的关键设计参数通常与该设计中的其他方面相关联, HDI PCB也不例外。在这种情况下,其控制因素是BGA的焊盘尺寸和节距。 通过表1我们可以看出焊盘尺寸与可能的走线宽度之间的关系,具体取决于焊盘之间通过的走线数量。对于“简单”或低I/O数的封装(图6a),我们只需要在BGA焊盘之间布一条走线,很明显最大走线宽度是焊盘之间可用空间的1/3。在给出的实例中,焊盘节距300mm,焊盘直径为150mm,因此建议的线宽和线距要求为50mm。 表1:指定焊盘尺寸所要求的线宽/线距 图6:走线对尺寸的影响(来源:Altera) 如果我们现在使用一个更复杂的封装,其更多的I/O数要求在同样的焊盘节距内布两条走线,那么推荐的线宽/线距就会下降至30µm,并且很明显,随着焊盘节距的减小,将进一步限制线宽和线距。 总的来说,新激光工具的可用性将允许更小的微通孔更密地排列在一起。这将有助于采用更小的BGA焊盘,与更多的 I/O数器件相结合,减小线宽/线距的需求,这将推动HDI路线图(图7)的发展,并继续从现有的每层生产布线转变为半加成法工艺。 图7:HDI路线图中的关键因素(资料来源:IPC、JISSO、AtoTeCo、客户群) ELIC、任意层和半加成法 目前大多数HDI PCB使用减成法ELIC(每层互连)或任意层技术进行生产。 一般流程如图8所示。 图8:ELIC工艺流程的通用示意图 高端HDI PCB需要线宽/线距从40 mm下降到30 mm,而目前的电镀工艺无法实现这一目标,因此需要转换到半加成法工艺。由于这些工艺在IC载板生产中很常见,因此HDI板被称为类载板的PCB(SLP)。 图9显示了基于半加成法(mSAP)工艺的SLP生产通用工艺。 图9:基于mSAP的类载板工艺的概要示意图 工艺挑战 很显然,半加成法(mSAP)工艺与传统的PCB生产路线有相同的步骤,因此原则上,更新和扩展现有设施使从减成法生产到半加成法(mSAP)生产的转变显得相当简单。然而,由于涉及许多变化,这种观点通常是错误的,从最近正进入类载板供应链的公司已经证明了这一点。必须为半加成法(mSAP)工艺量身定制的新设备和流程,同时在进行投资时充分考虑半加成法(mSAP)工艺的预期生命周期问题。幸运的是,这些可以修改为改良型半加成法(amSAP),该方法可以实现>20 mm 的线宽/线距,并且只需要有限的进一步投资。 表2: PCB生产工艺要点对比 表2显示了可用技术的简单对比,包括其性能和主要差异。 对于那些希望进入类载板供应链并开始提供电路板的公司,存在许多需要克服的挑战,其中有些可通过投资得以解决,而其他挑战只能通过与经验丰富的供应商合作来解决。 改进的激光钻孔 优化的PTH 图形电镀铜 细走线形成 改进层粘接 高分辨率表面涂层 总结 随着越来越多的移动设备设计师希望利用FOWLP和其他直接连接封装类型的优势,新一代HDI PCB已经在市场上出现。这些类载板PCB采用最新的高端制造工艺和材料,基于半加成法(mSAP)技术,可使线宽/线距小于30μm,来实现高端HDI的新一代变革。 化学药水和原材料供应商正在重新调整封装行业的工艺和产品,以适应新SLP领域的要求,而潜在的SLP生产商正在审查他们现有的工艺并决定是否投资。由于一些人将不可避免地反对投资,未来的SLP供应链中参与者数量是否有限?是否会存在风险?只有时间才能告诉我们答案。面对高端HDI市场再次来临的新挑战,有一点是可以肯定的——我们会奋起迎接挑战。 更多内容在线查看。