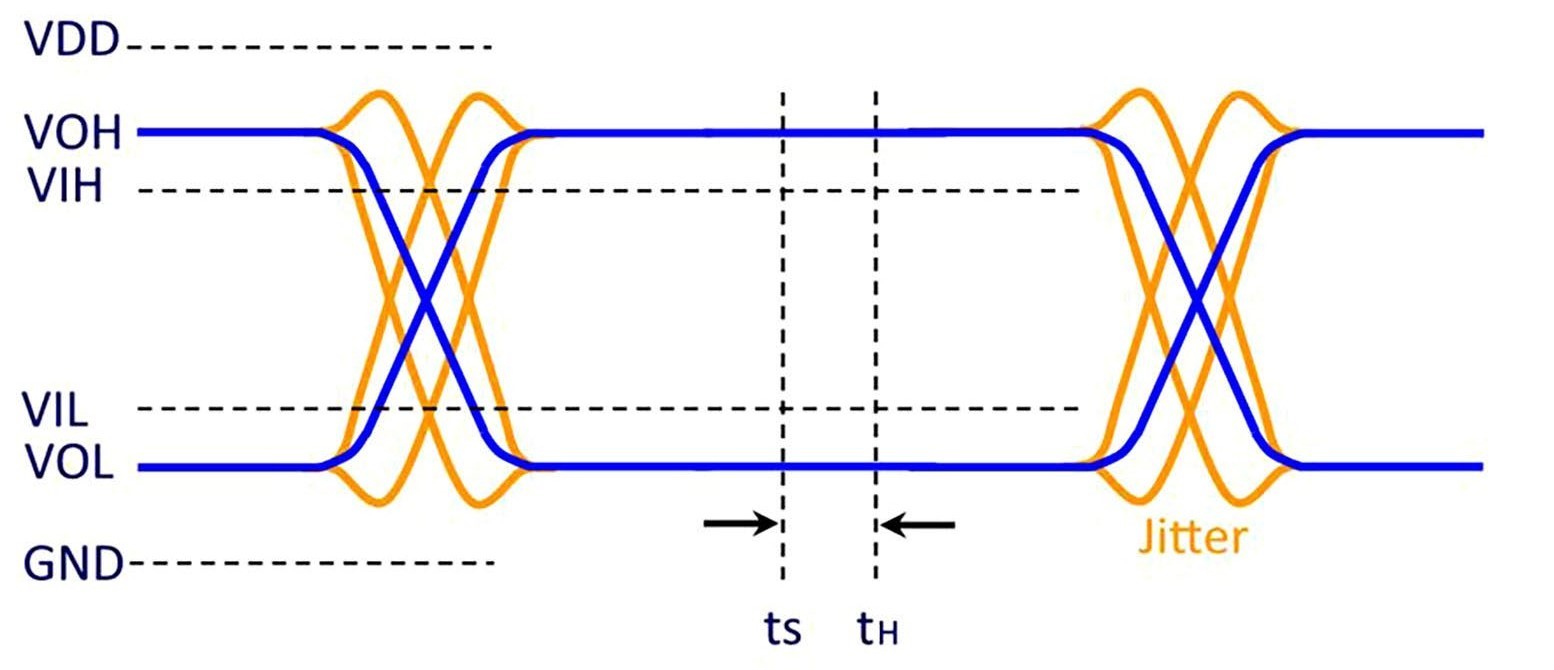

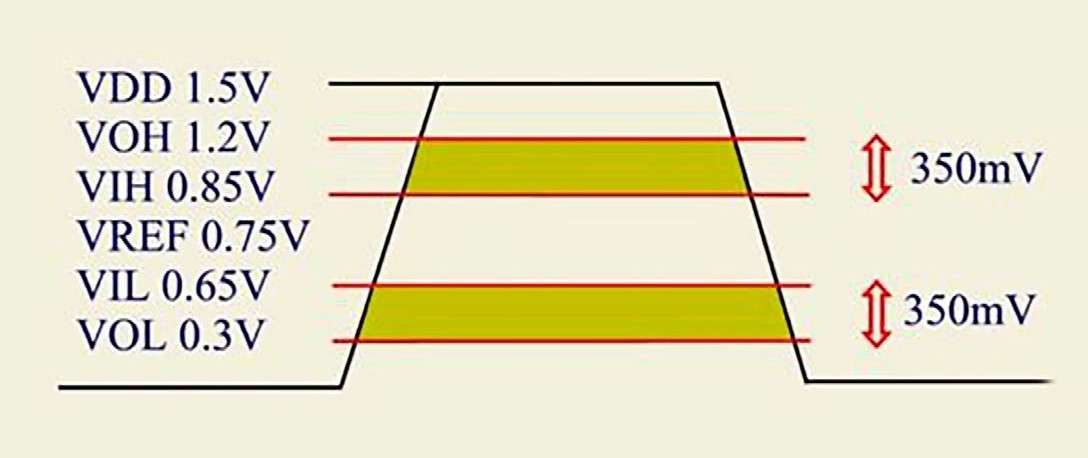

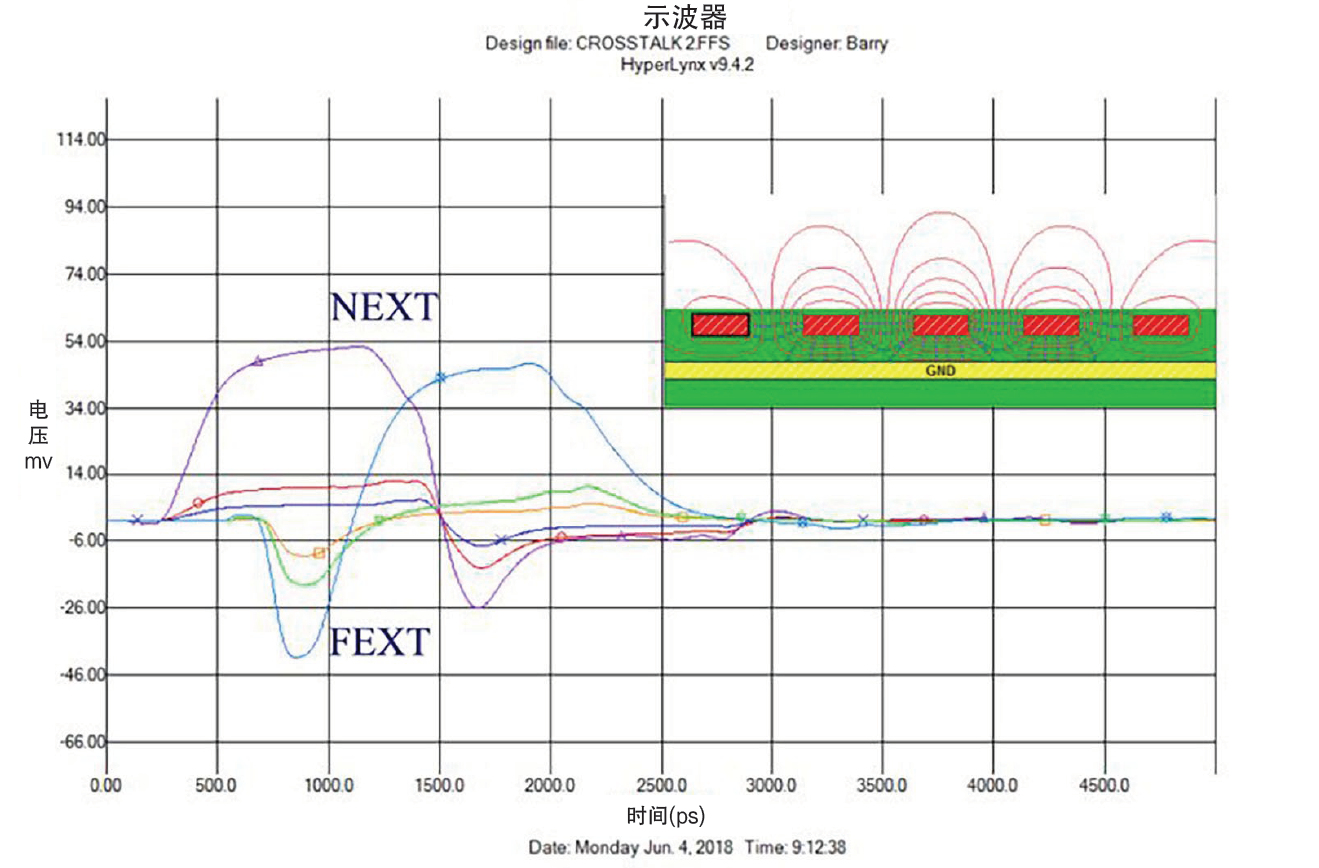

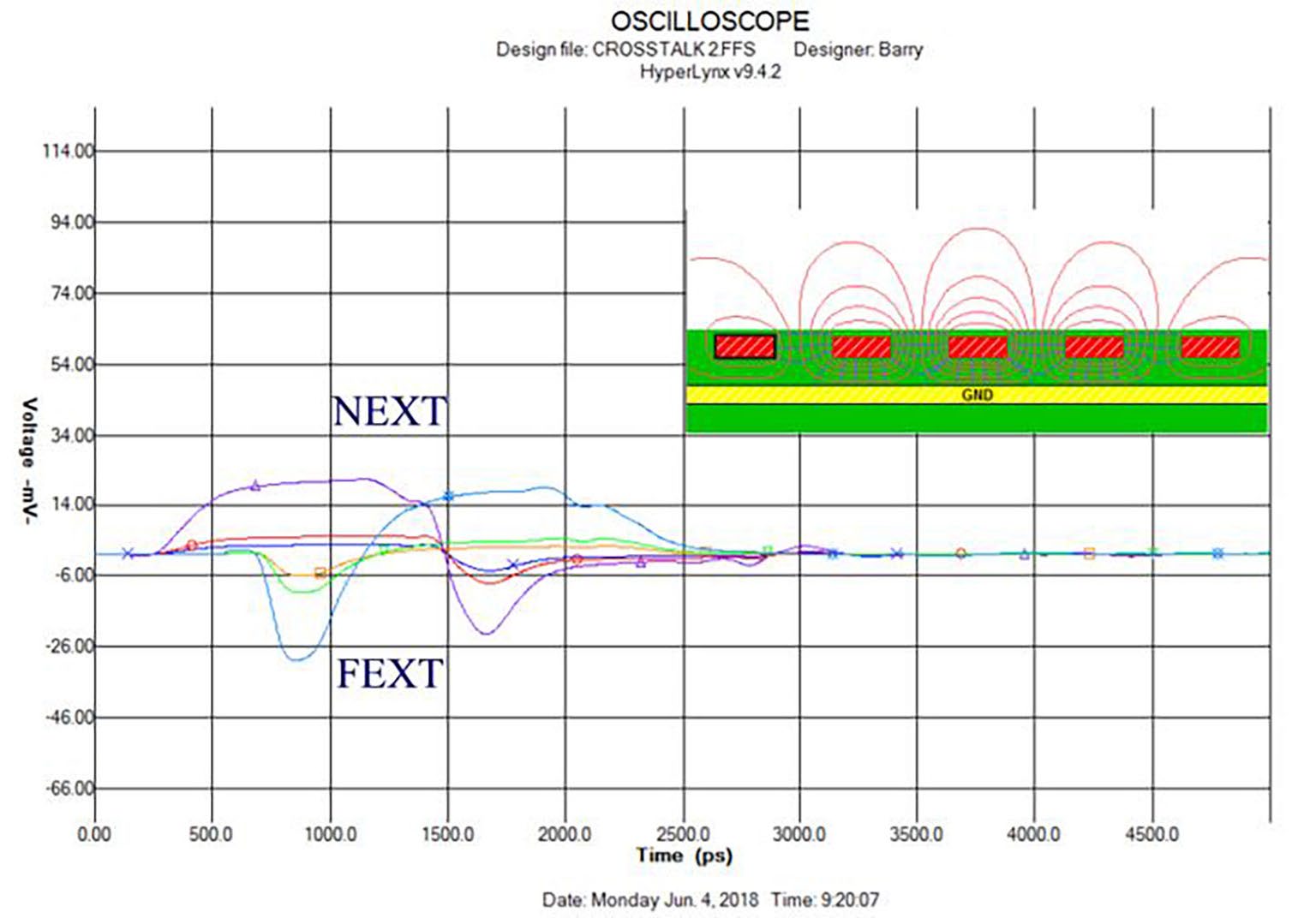

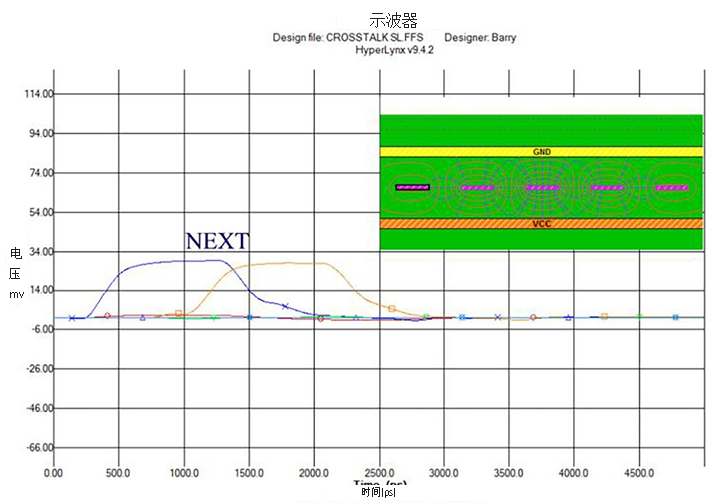

哪种程度的串扰是可以接受的?这取决于此PCB所采用的技术。我们已从多年前的TTL逻辑器件发展到今天的高速Gbps器件,可接受的串扰程度发生了巨大变化。CPU的功率,也就是它的发热量,是输入电压和电流的乘积。大趋势是降低核心电压,从而节省电力。但是,降低核心电压也会降低噪声容限。本期专栏文章将深入探讨可接受的串扰阈值以及如何减轻其对高速设计的影响。 串扰是由电磁场耦合引起的。电场会使信号电压容性耦合到附近的布线中。容性耦合会引发驱动电流浪涌,从而导致传输线上的反射。同时,磁场会导致信号电流被引入附近的布线中。感性耦合会产生地弹和电源噪声。串扰会按照距离的平方迅速下降,其影响程度与引发串扰的信号电压、可用的电路板空间以及信号布线的接近度有关。串扰可以表现为远端正向串扰(FEXT)或近端反向串扰(NEXT)。 图1:信号转换期间的串扰仅会导致眼图的抖动 幸运的是,通常用在并行数据信号传输的同步总线对串扰有非常高的抵抗力。串扰仅在信号切换时发生,并且该串扰仅会在时钟开启瞬间的一小段窗口范围内产生影响。必须在接收端的设置(tS)和保持(tH)窗口期间指定这个串扰。在此间隔期间,串扰决不能将任何有效信号驱动到相反的逻辑状态接收阈值以上。因此,在对总线进行采样之前,如果接收端等待足够长的时间,串扰就会稳定下来,就不会对接收端的信号质量产生影响。如果在信号转换期间串扰到来(图1),那么唯一影响就是眼图的波动。但是,这仅适用于同一组内的信号。另一方面,异步和不相关信号始终对串扰敏感。 但是,由于数字信号的速度不断提高,人们可能无法等待这么长时间来采样总线。随着电源电压从3.3 V降至1.5 V,允许的噪声容限降低超过一半,这使得电路设计人员对串扰的决策更加重要。串扰产生的噪声会侵蚀噪声容限。这种噪音可能不会太大,本身不太会导致故障,但足以使总噪声达到危险的临界值。 例如,对于DDR3内存器件,以下数值是JEDEC标准JESD79-3E中规定的: 图2:DDR3内存的噪声容限 最大串扰值是由接收端的预期电压与接收端阈值之间的差值决定的。在本文的实例中,最大串扰为350 mV,适用于单端信号。差分技术没有单端技术中的噪声容限问题。这是由于共模抑制效应,即接收端可以抑制两个输入上同时出现的噪声的能力。尽管差分技术在抑制输入噪声方面要好得多,但也并不是完全免疫。过度的噪音仍然可能会导致严重故障。 此外,串扰还取决于负载,在驱动存储器块时负载可能会显著变化。切记,每条受影响布线上的总串扰来自附近多个串扰源的串扰,所有这些串扰累加起来达到了最大值。 图3:4 mil /4 mil线宽/线距的微带线的近端和远端串扰 图3展示的是与串扰源布线(1.5 V @ 1 GHz)相邻的受影响布线的近端和远端串扰。在本实例中,布线宽度为4 mil,间距为4 mil,阻抗为40 Ω。但是,随着受影响布线距离串扰源越来越远,串扰也会减少。 图4:4 mil /8 mil线宽/线距的微带线的近端和远端串扰 图4展示的是宽度为4mil,间距为8mil,40 Ω阻抗的布线的近端和远端串扰。距离越远,串扰越少。但是,如前所述,受影响布线上的总串扰是附近所有噪声源导致的累积噪声,因此串扰结果可能会更高。 在微带线结构中,相邻布线之间的互电容耦合通常弱于互感耦合,从而使得FEXT系数为负值,这跟我们在先前的仿真中所看见的情况一样。但是,带状线结构不存在正向串扰。电感耦合串扰和电容耦合串扰之间的精细平衡几乎不会产生可观察到的正向串扰。 前面的例子是外层微带线结构,让我们来看看内层带状线的串扰情况。图5展示的是4 mil /4 mil线宽/线距、40 Ω阻抗布线的带状线结构的近端串扰。请注意,噪声中没有FEXT部分。而且,串扰的幅度峰峰也大大降低。因此,在所有其他因素相同的情况下,这就是为什么人们始终应该在多层PCB的内层上布置高速信号的另一个很好的理由。 在这种方法中,可能会被忽略的一个因素是对从第1层传输到第3层的信号产生的影响。在电路板上的那一点,存在于平面之间的任何电源噪声都会进入存储器总线电路布线。这有可能会成为串扰的主要来源,取决于配电网络(PDN)去耦的有效性。跳转位置的PDN噪声过大可能会完全抵消布线布局带来的串扰改善。这也是PDN分析和优化如此重要的另一个很好的理由。 图5:4 mil /4 mil线宽/线距的带状线的串扰 为了评估串扰,我通常会在Mentor Graphics HyperLynx中运行初步批处理模式仿真。在仿真中设置默认IC特性、最大串扰为150 mV和FCC B类的EMC。批处理模式仿真会自动扫描整个PCB上的大量网络,标记信号完整性、串扰和EMC热点。如果需要的话,还可以通过进一步的交互式仿真来评估报告中的串扰冲突。将仿真的所有信号设置为150 mV最大串扰可能看起来非常低,但它能确保我们能找到累积起来可能会对信号完整性造成致命危险的所有耦合。我还将此约束条件应用于同步总线中,以识别来自所有串扰源的总串扰影响。在早期消除噪声源比在产品开发过程的后期解决问题更容易,成本更低。 通过将干扰源与受影响布线分开,或通过减小平面上方/下方的电介质厚度,都能够减小正向和反向串扰。后者还需要减小布线宽度以保持阻抗不变。切记,低于4 mil的布线宽度通常会增加制造成本。因此,如果板面空间比较拥挤,尤其是高速设计,那么降低介电层厚度可能是一个很好的解决方案。我们无法完全消除串扰,但作为PCB设计师,我们的工作就是要确定如何控制、管理并承担我们决策的后果。 关键点: • 降低核心电压也会降低噪声容限; • 串扰是由电磁场耦合引起的; • 串扰会按距离的平方迅速下降,并且影响程度与噪声源信号电压以及接近程度有关; • 同步总线对串扰有非常强的抵抗力,它仅会在时钟开启瞬间的一小段窗囗范围产生影响; • 如果电源电压从3.3V降至1.5V,则允许的噪声容限降低超过一半; • 差分技术没有单端技术的噪声容限问题,原因是共模抑制; • 受影响布线上的总串扰是附近多个串扰源的总和; • 带状线结构不存在正向串扰,串扰的幅度也会显著降低; • 仿真应将所有信号的最大串扰设置为150mV;除非频率非常高,否则可以忽略同步总线内同一组信号的串扰; • 通过将干扰源与受影响布线分开或通过缩小平面上方/下方的电介质厚度,可以减少正向和反向串扰。 Barry Olney:In-Circuit Design Pty Ltd (iCD) 总经理 更多内容可在线查看。