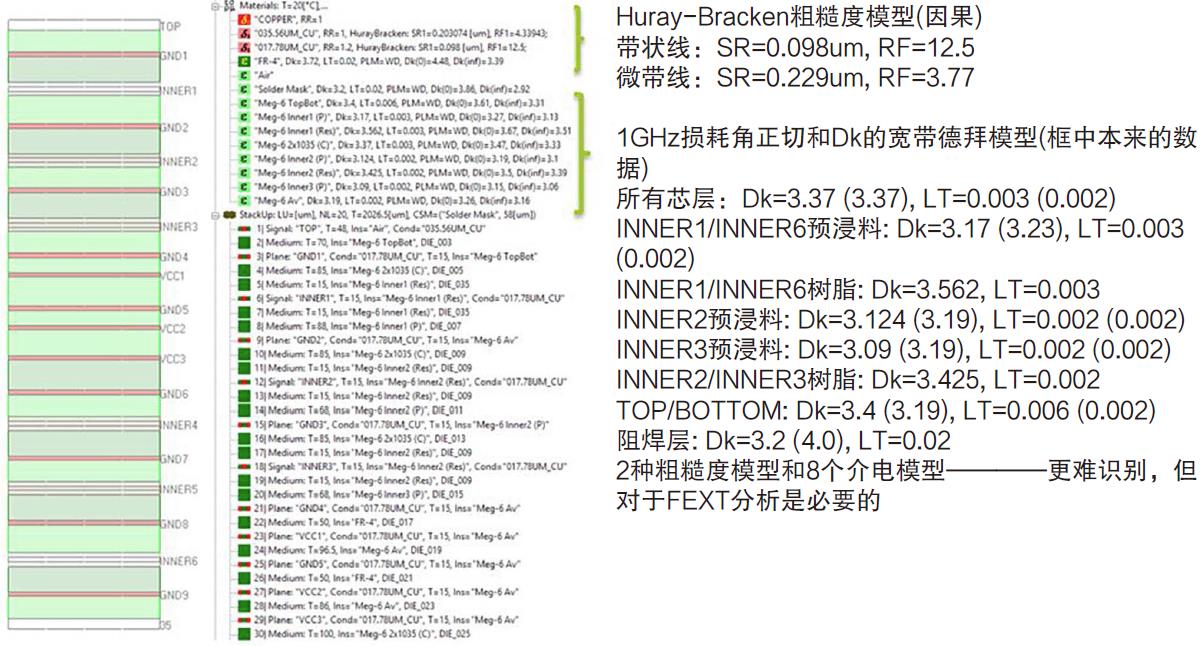

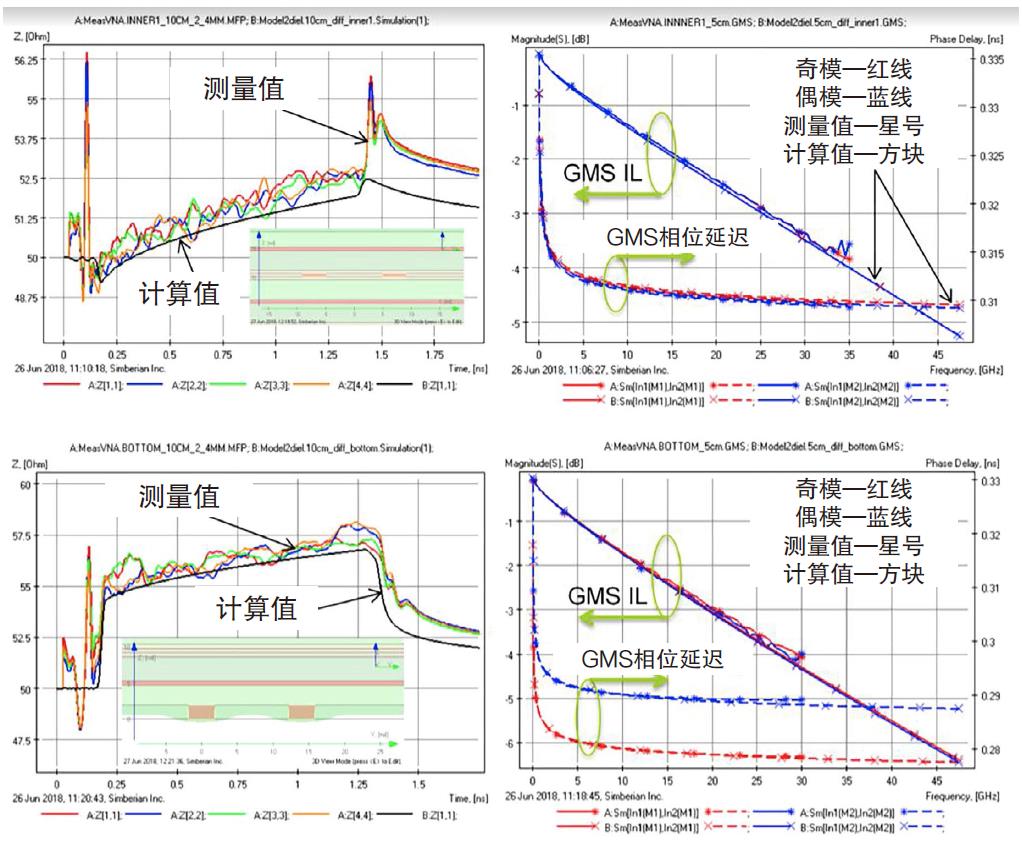

典型的PCB设计通常是从材料选择和叠层定义开始的,也就是叠层规划或设计探测阶段。材料供应商和PCB制造商提供的数据是否可靠?我们是否可以使用这些数据来预测布线宽度和间距,以达到目标布线阻抗,并计算延迟和预估损耗? PCB布线中通常会用到这些初步数据。PCB制造商可以进一步调整实际叠层以及布线宽度和间距,以达到目标阻抗。这通常是一个由阻抗来决定的过程,技术已经非常成熟,并且一般都能达成可接受的结果。 那么损耗呢?我们是否可以使用上述的初步数据来评估损耗以及与损耗相关的合规性指标?或者我们是否可以像阻抗一样指定目标损耗,然后交由制造商去操心?我们以EvR-1验证板的初步数据和最终数据为例来说明。该板的所有数据均由Infinera公司的Marko Marin提供。该验证板在我们的获奖论文《期望与现实》中也有出现。我们使用了Simbeor软件作为叠层探测工具,用于评估特征阻抗、延迟和损耗的准确性。之所以选择Simbeor进行叠层探测,是因为它可以进行高达50 GHz的系统化验证测量。 堆叠规划一般是从选择PCB制造商和可能的材料以及定义堆叠结构开始的。案例中的验证板有20层,其中8层分配给高速信号,如图1所示。验证板选用了低损耗的Panasonic Megtron6层压板来布线高速互连,同时,为PCB制造商指定了目标阻抗,制造商提供了预期的叠层结构、布线宽度和间距调整,以满足目标阻抗要求。批量化PCB生产一般都是这样操作的。 根据制造商的说法,预期阻抗变化应该在8%以内。对于高达30 GHz的28 Gbps NRZ链路来说,这太大了,无法达到良好的相关性,但也是可以接受的。电路板制造商提供了如图1左侧所示的叠层几何结构,图1右侧展示的是Simbeor软件输入相应叠层进行预布局的分析结果。Megtron6的规格表提供了多个频率下的介电常数和损耗角正切——只需一个频率数据就能够确定因果宽带德拜模型。图1中Dk的值与Megtron6规格表中的值略有不同,是由PCB制造商根据他们过去使用该材料的经验给出的。 图1:左图是来自PCB制造商的EvR-1验证板叠层和初始材料模型,右图是在Simbeor软件中为制造前分析定义的完全相同的叠层 这里的主要问题是导体的粗糙度模型——我们只知道铜箔粗糙度被指定为H-VLP,而没有其他数据。PCB制造商会在电路板制造过程中将铜箔的光面处理得更加粗糙,这一步也没有任何电气建模参数。即使我们有来自铜箔制造商的铜箔配合面的数据,PCB制造商对光面的处理也使它变得几乎无用。因此,我们只能在没有导体粗糙度模型和PCB制造商提供的布线调整的情况下开始叠层探测。有篇论文中详细介绍了EvR-1验证板设计的其余部分。为了验证初步数据,我们使用了在带状线层INNER1和微带线层BOTTOM中的10 cm差分链路(图1)。第一个实验的结果如图2所示。左图显示了测得的TDR,响应是用S参数计算得出的,最高到50 GHz。为了进行对比,图2还展示了在Simbeor中计算出的10 cm传输线建模的TDR。 图2:使用来自PCB制造商的INNER 1层(上图)和BOTTOM层(下图)叠层结构和材料参数,测量和计算出的10 cm差分链路TDR(左图)和GMS插入损耗(IL),以及测量和计算出的5 cm差分链路相位延迟(右图) 可以看到,带状线TDR的相关性是可以接受的,但微带线计算得出的阻抗要低得多。这些初步数据建模并不太准确。图2中,右图显示的是5 cm的差分链路测量和计算出的广义模态S参数(GMS参数)之间的相关性。GMS参数是无反射传输参数,在Simbeor软件中完全去掉了反射损耗。这使得这种类型的S参数成为了精确的材料参数识别和建模质量评估的理想选择。从GMS参数中,我们可以观察到建模的延迟偏差小于2 ps /英寸。这里,损耗出现了显著差异——在5 GHz时,差异就已经很大(约20%),在30 GHz时可能会变得完全不可接受(约50%)。 那么,为什么测量和建模之间存在如此大的差异呢?对于损耗而言原因显而易见,即我们在叠层探测阶段没有任何数据可以用于指定导体粗糙度模型。如果使用此类模型来计算合规性指标,可能会导致设计完全不能用! 注意,这不仅仅只跟损耗有关,它还会影响诸如插入损耗串扰比(ICR)等这类参数。对于阻抗和延迟的差异而言,原因有可能是横截面的几何形状或介质层的参数或两者皆有,在本文的后面会提到。让情况更加复杂的是,导体粗糙度还会增加布线的电感,除了损耗之外还有可能会显著改变阻抗和相位延迟。所有这些都必须包含在传输线建模中。此外,对建模参数(几何或介电特性)进行简单调整没有作用,参数实在太多,需要采用系统化方法。幸运的是,使用Simbeor软件,可以系统化地分别识别出电介质和导体粗糙度模型的参数。 可以使用测量出的两段线路的S参数来完成建模,并将其转换为GMS参数,或转换为复杂传播常数(Gamma)。GMS参数和Gamma均可在Simbeor中通过分离介质和导体粗糙度的损耗来识别材料特性。为了准确识别,必须进行横截面检查,测量出待测结构中的传输线几何形状。我们对EvR-1板进行了横截面检查。最终的布线宽度和间距以及横截面的示例如图3所示。 图3:最终的布线几何调整以及INNER1和BOTTOM层中的待测差分链路的横截面示例(期望值数据来自PCB制造商) 我们可以从中了解到的是,这家PCB制造商对带状线的布线宽度和间距调整尚可接受,BOTTOM和TOP层中的微带线布线的几何形状则与制造商提供的数据完全不同。这就是图2中我们观察到的微带线TDR差异较大的原因。 通过显微照片的所有几何调整,Simbeor软件识别出的电介质和导体粗糙度建模的最终叠层如图4所示。为了确保精度,我们用了8种介电模型,其中1种用于核心电介质,4种用于预浸料层,1种用于阻焊电介质,以及2种可选的,用于内层中的围绕带状线的树脂富脂区。仅当测试结构中存在远端串扰(FEXT),并且必须在建模中考虑到时,才需要用到树脂富脂区。图4括号中展示的是PCB制造商提供的介电常数和损耗角正切,以供比较。除了电介质之外,我们还确定了两种导体的粗糙度模型,不过没有什么数据可以用于比较。所有的调整和材料建模与测量值的相关性分析如图5所示。与图2中的PCB制造商提供数据的结果相比,图5的相关性要好很多。但是,由于在制造过程中会有预期变化,以及我们可能会进一步发现其他的未知原因,它还不完美。通过这种新的叠层方法,布局前和布局后分析都可以达到高可信度。 图4:最终叠层结构、介电层和导体粗糙度模型 我们的结论是,必须验证PCB制造商提供的叠层数据。将来自该制造商的带状线层数据用于初步分析带状线中的阻抗和延迟基本上是可接受的。但是,表面层(微带线层)中的布线数据不能用于进行任何分析。最令人不安的是没有模型或任何有用的数据来建立导体的粗糙度模型,没有这些模型,对损耗的任何计算都毫无用处。因此,在整个叠层探测或规划阶段都必须包括构建小型验证板或测试样品,以验证从PCB制造商处获得的数据,并识别出实际几何调整和导体粗糙度模型。样品应具有两段传输线(单端或差分),每层具有不同的长度和不一样的电介质。在测量线段的S参数之后,必须对样品进行横截面切割。这是设计可预测互连的系统化方法中最重要的一步。 图5:左图为测量和计算出的10 cm差分链路的TDR和GMS插入损耗(IL),右图为测量和计算出的5 cm差分线段的相位延迟,上下图分别为识别出的INNER1层和BOTTOM层的叠层结构和材料模型。 本文中的所有计算都是使用Simbeor软件完成的。 更多内容可在线查看。 Yuriy Shlepnev:Simberian Inc. 创始人兼总裁