地弹,或者应该更准确地描述为电源反弹,指的是电源传输路径中两点之间产生的电压。它与电流路径和共享回路的总电感以及电源供电产生的瞬时浪涌电流有非常密切的关系。在这个问题中,电感再次成为高速PCB设计师的敌人。这是导致同步开关噪声和电磁辐射的主要原因。随着信号边沿变化率不断提高,对固有电气特性所造成的影响也变得更加明显。这些固有特性之一就是所有IC的电源引脚上的电感。在本篇中,我们将着眼于电源反弹以及如何使其对高速数字电路的影响降至最低。

图1:地弹可能比跳投更难控制

地弹是由IC芯片基板与PCB接地返回平面之间的共模电位产生的,并且与传输线特性完全无关。其他会产生影响的因素还有IC内器件驱动端的物理位置,以及与连接到芯片的公共电源和接地连接有关的同步开关的输出数量。另外,地弹还与输出的dI / dt(一定时间段内的电流变化)有关,取决于驱动端门的开关速度。

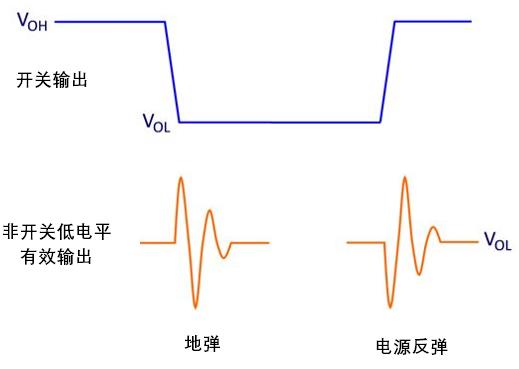

图2:输出电压与电源反弹

如图2所示,地(GND)弹由信号的高到低转换产生,而电源(VDD)反弹是由低到高的转换产生的。CMOS器件的输出缓冲级通常是反相器,因此,当输入从高电平切换至低电平时,输出会从低电平切换至高电平,反之亦然。地弹就是由切换输出晶体管相关的电流产生的。请注意,这里讨论的与地弹有关的所有内容同样适用于完全相反的电源反弹。

当发生电源反弹时,电源传输路径上产生的电荷会导致共模电压。不幸的是,无法消除逻辑转换产生的电荷转移,但是通过在电源和地之间提供一条交流阻抗非常低的路径来限制辐射峰值的幅度。这就是配电网络(PDN)规划如此重要的原因。电源平面的交流阻抗必须保持低于最大带宽的目标阻抗。

与输出信号的全轨电压摆幅相比,测得的电源反弹一般非常小(通常为150 mV)。所以,它的存在不会影响信号传输。但是,它会干扰负载端信号的接收(具体取决于噪声容限),并可能导致双时钟。这是因为TTL接收器会将输入电压与本地0V接地参考平面进行比较,CMOS器件会将输入电压与VDD和GND的加权平均值进行比较,而ECL会将其与VDD进行比较。虽然各类逻辑的拓扑结构不同,但电源反弹的概念是相同的。如果N个输出同时切换,就会产生N倍电流,电源反弹脉冲就会增大N倍。

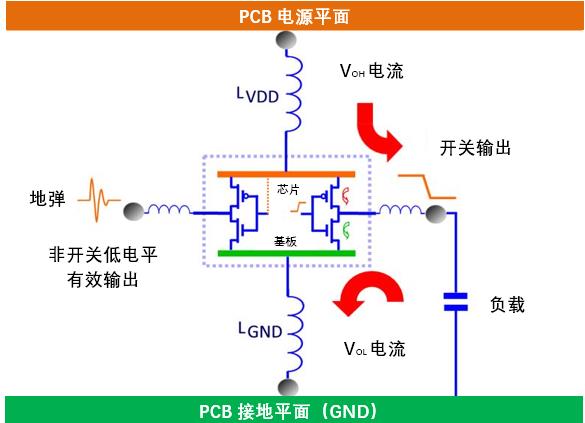

图3:BGA封装中电源反弹的产生

图3展示的是电源反弹产生过程的简单视图。当驱动端晶体管(右侧)的输入变成高电平时,输出变成低电平(VOL),此时,就会通过BGA封装的输出球从容性负载中引出一个浪涌。该电流会流过由BGA封装下方的接地球矩阵构成的电感LGND,导致IC芯片基板上的电压波动。通常,BGA封装上会有多个GND和VDD焊盘,因此,并联组合起来可以降低LGND和LVDD的整体电感。受到影响的非开关输出(左侧)会保持低电平有效状态。然而,基板上的电压波动会耦合到输出中,并且通过引脚传输出去。IC上可能会有数百个这样的输出,这些输出都同时将开关噪声传递到平面上。VDD反弹的情况正好相反,当输出开关拉高输出电压(VOH)时,电流会通过LVDD冲击负载。

在提高PDN电流时,以下情况会导致电源反弹更加严重:

- 容性负载增加

- 负载电阻降低

- 引脚和走线电感增加

- 多个门同步开关

在高速情况下,IC封装的引脚电感至关重要。较大的封装往往具有更高的引脚电感。引线键合、带式自动键合(TAB)和倒装芯片封装通过缩短IC芯片基板和PCB平面之间的电源引线连接,大大降低了内部电感。

幸运的是,对于PCB设计人员来说,特别是在PCB布局和布线过程中,可以使用很多方法,最大限度地降低供电路径中的电压下降,从而减弱电源反弹。方法如下:

- 降低回路中的变化速率。在可能的情况下,可以通过使用串联电阻来降低边沿速率。此外,除了用芯片内的匹配电阻外,一些IC现在还具有时钟偏移调整功能,二者可共同降低信号边沿变化速率,同时还可以减少对外部匹配电阻的需求。

- 降低返回路径的回路电感,返回路径尽可能短而宽。

- 将信号和返回路径放在一起。这样会增加耦合,并确保返回路径和信号路径的回路面积最小。

4.限制使用相同返回路径信号的数量。在封装扇出布线时,应该为IC的每个引脚提供单独的接地和VDD连接,直接连接到接地或电源层。将两个或多个引脚连接在一起,然后将它们通过相同的线路连接到共用的接地通孔,会与采用多个接地和电源引脚的目的相悖。

5.通过使用宽平面而非厚走线,最大限度地减小布局过程中的平面电感。

6.在电源层和接地层之间使用薄(小于5 mil)的电介质芯材料。或者更好的方法是,使用嵌入式平面电容为IC提供额外的低电感去耦。

7.通过分析整个频带宽度的去耦要求来优化配电网络。低交流阻抗会减少辐射。

8.在可能的情况下,将电源和接地通孔相邻放置,抵消掉彼此的磁通量,从而最大限度降低共模电流。

9.最好选择下方中央有一个大接地焊盘的IC封装,并使用多个通孔连接它,以减小对地电感。另外,请选择接地和电源引脚与信号引脚比率较高的封装。BGA通常都能达到这些要求,但其他SMT封装的电源引脚数量就很有限。

10.在能提供所需性能的条件下,选择驱动电流输出最小的IC。这样就能减少快速充满系统电容的电流量,从而直接减少地弹。

11.错开设备上输出引脚的时序。通过在较长时间内延长许多输出的开关时间可以大大减少IC级地弹。

12.使用差分信号并避免共模电流。差分模式会在双线出现不平衡时转换为共模,所以最好是通过增加额外长度的方式也就是延迟,来纠正差异。

由于不能完全消除电源反弹,当组合振幅变得过大时,就会出现问题。然而,低电感和低交流阻抗的配电网络可以降低高速数字PCB设计中的同步开关噪声和电磁辐射影响。

要点

- 电源反弹与电流路径和共享回路的总电感关系非常密切。这是造成同步开关噪声和电磁辐射的主要原因。

- 发生电源反弹时,电源输送路径上施加的电荷会产生共模电压,而这种共模电压又会产生电磁辐射。

- 为电源和地之间提供一条交流阻抗非常低的路径,可以限制辐射峰值的幅度。

- 电源反弹会干扰负载端信号的接收(具体程度取决于噪声容限),并可能导致双时钟。

- 增加引脚电感、容性负载和同步开关输出,会导致电源反弹变得更加严重。它也会随着电阻负载的降低而恶化。

- 在高速情况下,IC封装的引脚电感至关重要。较大的封装往往具有更大的引脚电感。

- 在PCB布局和布线过程中可采用多种方法,可以使用很多方法,最大限度地降低供电路径中的电压下降,从而减弱电源反弹。

参考

- Barry Olney’s Beyond Design column,The Dumping Ground.

- Understanding and Minimizing Ground Bounce, Fairchild Semiconductor.

- EMC and the Printed Circuit Board, Mark Montrose.

- Signal and Power Integrity – Simplified, Eric Bogatin.

- High-Speed Digital Design, Howard Johnson.

Barry Olney是澳大利亚In-Circuit Design Pty Ltd (iCD)的常务董事。该公司是一家PCB设计服务公司,专门从事电路板级仿真服务。iCD开发了iCD Design集成软件,其中包括iCD Stackup和iCD PDN 和CPW Planner软件。请访问www.icd.com.au了解详情。阅读往期专栏或联系Olney,请点击此处。