在低频下,PCB上的布线和元件属于无损集总元件——摘自《电路理论101》。但随着频率增加,铜布线和相邻的介质就会为传输线,趋肤效应会迫使电流沿导体外表区域流过,根据频率变化的损耗也会对信号质量产生影响。在这种情况下PCB布线就表现为带有寄生电感和电容的分布系统,其特征是延迟和传播反射。我们现在担心的这种行为发生在频域,而不是比较常见的时域。这就是高速设计的真实情况。

图1:是理想情况下和实际情况下的上升沿对比

1)Time: 时间

2)Voltage: 电压

3)Ideal: 理想情况下

4)Real world: 实际情况

理想情况下,方波信号具有均匀倾斜的上升沿和下降沿。然而,在实际情况下,信号效果会大不相同。图1给出了两种情况下的方波上升沿,将理想情况下(低频)和实际情况下(高频)的结果进行了对比。传输线效应产生的下冲和过冲会导致信号出现振铃现象。如果振铃超过了电压输入高阈值(VIH),那么它在接收端就可能会造成误触发。

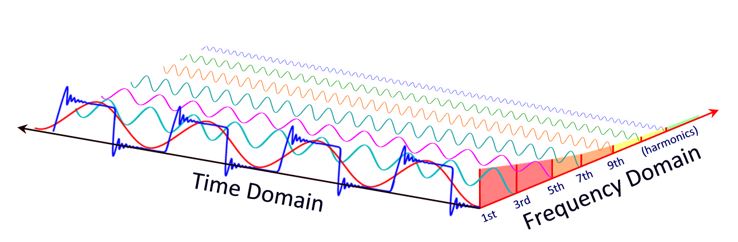

傅立叶定理表明,每个函数都可以表示为各种振幅和频率的正弦与余弦的和。方波的傅里叶级数展开是由奇次谐波的和组成。图2展示了方波从时域到频域的转换,以及频率分量的合成振幅。如果波形具有均匀的占空比,那么偶数谐波就会被抵消。方波的高频部分明显会受到波形上升时间的影响。同时,随着频率增加,振幅会减小。在实际情况下,需要考虑包括谐波在内的信号的最大带宽,而不是假设完美的方波基频模型。

图2:方波谐波从时域到频域的转换

1)Time domain: 时域

2)Frequency domain: 频域

3)harmonic: 谐波

令人惊讶的是,即使是频率很低的条件下,老式电信线会仅仅因为电线长度与信号上升时间相当所以变成了传输线。近年来,边沿速率变得快了很多,PCB上短布线的长度不到穿过PCB布线的边沿速率的2倍。所以要考虑到这些PCB布线会成为传输线,并且要分析它们的信号完整性。

总的来说,应该重视所有布线长度(以英寸为单位)等于或大于上升时间(以纳秒为单位)的驱动端,并且应该将这种布线当作高速传输线来对待。信号的上升/下降时间决定了关键的信号速度,而不是信号时钟频率。然而,在信号线上加载靠近源端的阻尼/反向匹配电阻可以缓解急剧升降的上升/下降时间。

阻抗是控制设计稳定性的关键因素——它是信号完整性和电源完整性方法论的核心问题。在低频下,PCB布线是理想的电路,因为它电阻小且不存在电容或电感。电流沿着电阻最小的路径流动。但在高频下,交流电路的特性导致电感和电容很普遍。电流沿着电感最小的路径流动。理想无损耗传输线的阻抗与电容、电感有关:

但这个公式过分简单化了,应该使用场解算器模拟阻抗,从而得出基板上每个信号层阻抗的准确值。布线的阻抗极其重要,因为传输通道上任何阻抗不匹配都会导致信号质量下降或可能引起噪声辐射。为了能量的完整传输,源端的阻抗必须等于负载端的阻抗。但通常情况并非如此,在边沿速率较快的情况下,常常要求端接来限制振铃。

高速设计中通常会使用50-60欧姆的特性阻抗。比这个数值低的特性阻抗会引起过度的dI/dt串扰,并且会使消耗的功率翻倍从而引起散热问题。比这个数值高的特性阻抗不仅会产生较高的串扰,还会让线路产生较大的电磁辐射和较高的电磁敏感度。但随着核心电压的下降,上升时间变得越来越快、频率也越来越高,更低的阻抗较为理想。比如,DDR3/4存储总线使用40欧姆的特性阻抗和80 欧姆的差分阻抗。

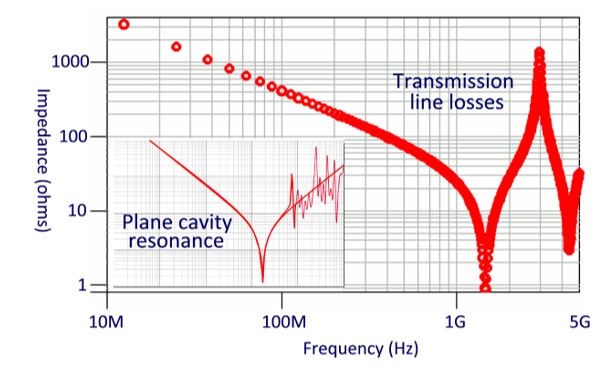

图3:使用矢量网络分析仪测量50Ω、1英寸长的布线(来源:Eric Bogatin)

1)Impedance: 阻抗

2)Frequency: 频率

3)Plane cavity resonance: 平面谐振腔

4)Transmission line losses: 传输线损耗

图3详细介绍了用矢量网络分析仪(VNA)测量得出的实际输入阻抗,是一条长1英寸的传输线,另一端为开路。这和平面孔腔谐振的AC阻抗十分相似,后者同样也没有端接。但是,平面对的面积更大,所以比布线的电容更大、电感更小,使得频率中的谐振更小并且提供了一条阻抗很小的路径。因此,平面类似大、厚没有端接的传输线。

传输线的特性阻抗设计为50 Ω,但随频率而变化的损耗会对信号质量造成影响。频域发射和反射的数据分别被称为插入损耗和回波损耗。特性阻抗(Z0)通常用来说明布线阻抗,被定义为无损耗传输线的瞬态阻抗。

最基本的信号完整性分析包括规定线路板叠层,其中包括适当的介电常数和层厚度,以及要确定符合布线目标特性阻抗和差分阻抗的布线宽度(和差分信号的间距)。而且,选择适当的阻抗及其他传输线特征对于生成精准结果是必不可少的。

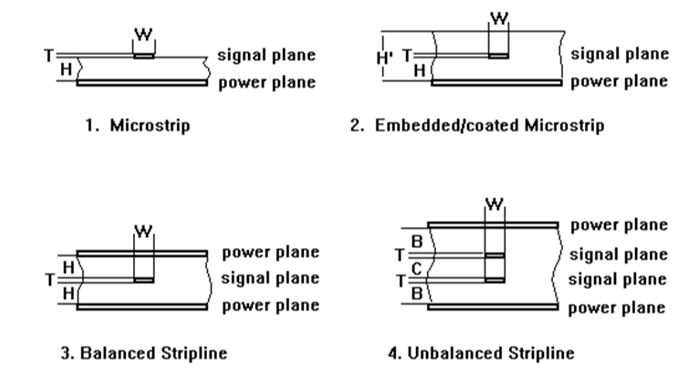

多层PCB非常适合于提供互连布线,这种布线是专门设计用于提供理想的阻抗控制。常用的方法通常采用微带线和带状线实现阻抗控制。传输线结构一共有4种基本类型,如图4所示:

- 微带

- 嵌入式微带(带有阻焊膜或敷形涂覆)

- 平衡带状线(也就是对称带状线)

- 不平衡/双嵌入式带状线(也就是不对称带状线)

图4:阻抗结构的4种主要配置(来源:IPC-2251)

1)Microstrip: 微带线

2)Signal plane: 信号层

3)Power plane: 电源层

4)Embeded/coated Microstrip : 嵌入式/涂覆式微带线

5) Balaned stripline: 对称带状线

6) Unbalaned stripline: 非对称带状线

值得注意的是,不同材料会展现出不同介电常数(Er或Dk)。举个例子,空气的Er = 1,铝增强板的 Er = 10,氧化钡的Er则高达600。标准FR-4的Er = 4,专门设计用于高速设计的介质通常具有较低的介电常数。比如说,Isola Astra-MT77 100GHz材料的Er = 3。介电常数会对阻抗和信号通过基板的传播产生直接影响。这就是为什么特定材料的介电常数要清楚地标识在供应商(或可靠来源)的技术规格中,上面要列出不同频率下的Er值。请注意数据表中一般用Dk表示介电常数。

基于闭合方程的阻抗计算器已经出现多年了,但它们的准确度十分有限。网上可以找到很多例子,但它们的结果一般都是粗略的估测,但它们在双重嵌入式(不对称式)带状线的计算上实在是错得离谱。IPC最早在IPC-D-317上发布了阻抗计算公式,之后在IPC-2251标准里也发布了这些公式。后者是以Brian C. Wadell所写的《传输线设计手册》为依据,但这些复杂的公式也未必能解决带状线结构中介质周围的宽度不平衡。因为阻抗是控制设计稳定性的关键因素,设计者永远不可以在高速设计中对要求的精度打折扣,而且必须要使用非常精准的场解算器。

在信号线上加载靠近源端的阻尼/反向匹配电阻可以缓解急剧升降的上升/下降时间。这种方式也可以让驱动端的阻抗与传输线的阻抗相匹配。但是,使用主流PCB布局软件时,使用者无法知道驱动器的阻抗是多少,更不要说让驱动器的阻抗与传输线相匹配了。相对于一般的50欧姆传输线,驱动端的阻抗通常都很低,但添加几个数值适当的电阻就可以解决这一问题。

是否需要端接一条PCB迹线是根据几项设计标准决定的。最重要的是电气长布线,当布线长度超过了上升沿速率电气长度的1/6时,就需要端接这条布线。但即使布线短,如果负载具有电容或高电感,那么就需要端接布线来防止出现振铃。串联端接对于点对点布线非常有效,每个网有一个负载。它对电气短的布线也非常有效,并且可以在不影响网内其他电路的情况下用来从同一个源端(呈星状布线)放射状扇出多个负载。串联端接可以减少振铃和地弹现象。它是高速设计中最普遍采用的端接方式。

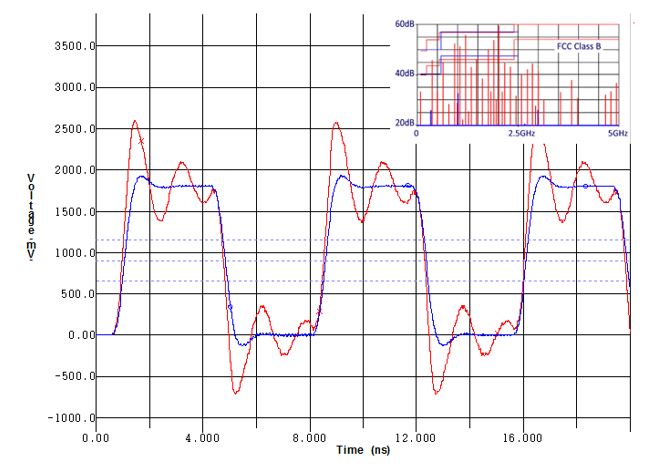

图5:通过添加串联端接负载,振铃现象大大减少(用HyperLynx完成模拟)

1)Voltage: 电压

2)Time: 时间

3)FCC Class B: FCC B级

回想一下现实环境中的上升时间边沿速率(图1),通过添加一个串联端接(靠近源端),将会大大减少振铃现象。这会减少串扰现象,同时可以消除辐射。在图5中,红色的波形是原始的有振铃的信号,蓝色波形显示出一个串联电阻的阻尼效应,它和理想的波形十分相似。插入的是频域中的预计辐射。

高速数字设计实际上就是控制阻抗。传输线的阻抗需要匹配,并且要在互连的整个长度中保持一个恒定值。同时,电源分布网络要提供一个阻抗较低的路径,该路径要贯穿各个平面和信号的整个频带宽。这些看似毫不相干的准则控制着产品的稳定性和可靠性。把这些做好,你的高速设计就可以有个不错的开始;如果没有落实好这几点,那你就会体验到现实世界的残酷。

要点回顾

- 在高频环境下,PCB导线就是一种带有寄生电感和电容的分布式系统,其特征是延迟和反射。

- 传输线效应产生的下冲和过冲会导致信号出现振铃现象。

- 方波的傅里叶级数展开是由奇次谐波的和组成。

- 当布线长度与信号上升时间相当时,一条布线就变成了传输线。

- 应该得到重视所有布线长度(以英寸为单位)大于或等于上升时间(以纳秒为单位)的驱动端,并且应该将这种布线当作高速传输线来对待。

- 阻抗是控制设计稳定性的关键因素;它是信号和电源完整性方法的核心问题。

- 为了完整能量的传输,源端的阻抗一定要等于负载的阻抗。

- 在边沿速率较快的情况下,需要采用端接布线的方式来匹配阻抗、限制振铃现象。

- 随着核心电压下降,上升时间变得越来越快、频率也越来越高,阻抗则越低越好。

- 传输线测量得到的输入阻抗和平面孔腔谐振的AC阻抗十分相似,后者同样也没有端接。

- 特性阻抗(Z0)被定义为无损耗传输线的瞬态阻抗。

- 最基本的信号完整性分析包括规定线路板叠层,这对生成准确结果十分重要。

- 专为用于高速设计而设计的介质具有较低的介电常数。

- 基于闭合方程的阻抗计算器的准确度十分有限,使用精准场解算器是十分有必要的。

- 可使用串联电阻来匹配驱动端和传输线的阻抗。

- 当布线长度超过了上升沿速率电气长度的六分之一时,需要端接布线。

- 高速数字设计实际上就是控制阻抗。

References

- Barry Olney’s Beyond Design columns: Controlled Impedance Design, Impedance Matching: Terminations,Signal Integrity Parts 1, 2 & 3

- What’s the Difference Between Signal Integrity and Power Integrity? by Patrick Carrier

- The Critical Length of a Transmission Line, by Eric Bogatin

- Bandwidth Basics, Wavelength Electronics

- IPC-2251–Design Guide for the Packaging of High-Speed Electronic Circuit

- High-Speed Digital Design, by Howard Johnson

Barry Olney,澳大利亚In-Circuit Design Pty Ltd (iCD)公司管理主管,该公司专门从事线路板模拟类PCB设计服务。该公司研发出了 iCD Design Integrity软件,软件包含iCD Stackup、PDN及CPW Planner。可点击www.icd.com.au下载软件。联系Olney或阅读往期专栏,请点击此处。