本文是《垂直导体结构》文章的第3部分。点击链接,可阅读第1部分《对顺序层压法的再思考——垂直导电结构》和第2部分《垂直导电结构VeCS与微加工》。Allegro PCB Editor是Cadence推出的先进 PCB 设计布线工具。

随着设计密度和复杂度的不断增加,有时需要设计师利用不同的导通孔技术对引脚数较多的器件进行布线,与此同时还要保证最高水平的信号完整性。采用通孔可能会占用大量宝贵的电路板空间。可是使用较小的盲孔虽然能够减小导通孔尺寸,却需要更大的埋孔来完成电路板较深位置的连接。另一种成本较高的替代方案是使用任意层互连(every layer interconnect ,简称ELIC)技术,也就是说每对层都有自己的微导通孔,这种微导通孔用激光钻孔,并填充了铜。在每对层之间的表面互相堆叠这些微导通孔可以扩展电路板内任意两层之间的连接。这些通孔技术能够成功完成设计的布线,但与此同时也会增加电路板层数,如果操作不当还会引起信号完整性问题。

新的垂直导体结构(VeCS )技术可以减少层数,并且无需顺序层压技术就可提升信号完整性。VeCS 与传统的通孔、微导通孔及ELIC设计不同,后面这三种技术成本高且需要多次层压、钻孔和电镀周期才能制造出合理的层数。使用VeCS技术可组合布线通道,更好地利用通道实现引脚数较多器件的扇出。更多的布线通道可以在更可靠/坚固的平面基准下实现更多的布线,不会出现其他通孔技术一般都会出现的问题。可访问https://www.nextgin-tech.com,了解有关VeCS技术的更多详情。

在Allegro 17.2中,VeCS结构就是一种机械符号。它可以被放在任何位置或放在球栅阵列(BGA)器件占位内来利用这项新的布线扇出技术。除了生产输出升级后要针对引脚生成有限深度(盲孔)钻孔文件来支持VeCS-2盲深度结构,不需要做出大的改动即可支持Allegro PCB Designer中的这些新结构。若在布局过程中使用了这些结构,17.2 Padstack Editor支持逐层及相邻层禁布区,以保证产品的可制造性。这些结构都可创建为库对象,所以在很多设计中对常用器件扇出布线时,很容易利用这些结构。如果一种结构需要改变,只需在一处进行改动,刷新后,整个布局中其他同类结构就可全部完成修改。

VeCS

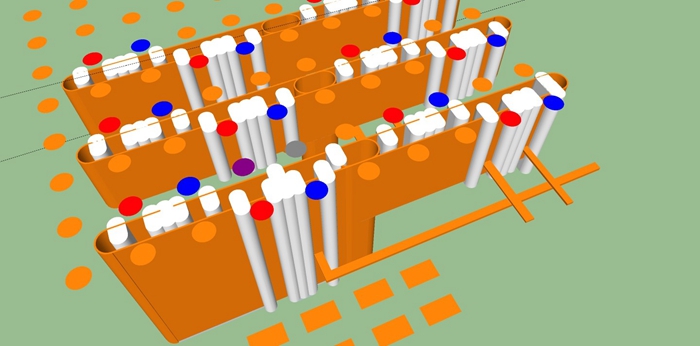

现在我们来区分两种“槽”技术:VeCS-1是指贯穿整个电路板的槽,VeCS-2是指电路板的多层盲槽(见图1)。

图1:左前侧的槽是VeCS-1,右侧的槽是VeCS-2

在实际应用中,我们会混合使用VeCS-1和VeCS-2结构。其优点在于我们可以用VeCS-1来实现GND及电源与多层的连接,例如,相邻的信号只连接到第4层。槽中的VeCS-2部分会产生残桩连接,最大程度地减小高速传输信号的容抗和分散。

目前,NextGIn Technology公司重点关注下一代产品,例如超高频带宽应用,其中两个层之间的信号从一层传输并连接至下一层时,可以进行调整,使垂直走线的阻抗与信号层阻抗相匹配。所以层之间的传输损耗降到了最低,与目前使用的传统导通孔技术效率低、成本高的点对点式布线相比,新技术可以更高效地利用布线空间。

VeCS可以和通孔、埋孔/盲孔、微导通孔/HDI技术结合使用,没有任何限制。例如,一个VeCS芯/多层可以被电路板表面和底部上下各一组微导通孔夹在中间。

目前所采用的工艺流程如下:

1. 按照标准流程生产电路板

2. 形成槽(可选在机械钻孔阶段):通过前钻和背钻构建VeCS-1和VeCS-2结构

3. 完成电镀(标准)

4. 填充槽和孔(可选)

5. 形成二次铣和底部铣

6. 填充槽(二次布线)

7. 钻贯通孔(可选)

8. 完成表面电镀,与塞孔电镀(plated over-filled via ,简称POFV)类似

9. 按照标准完成面板

制定VeCS的设计规则

适用于VeCS的规则与贯通孔/导通孔技术或HDI技术所采用的规则相同。图像重叠(孔环)如槽与铜的重叠、二次铣与槽的重叠等参数的正确设置非常重要。

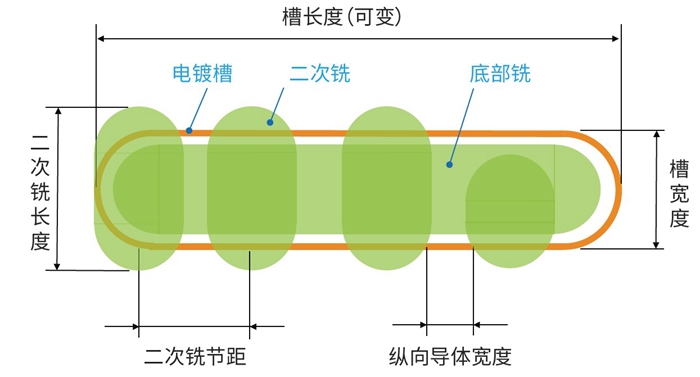

图2为VeCS要素的俯视图,以及VeCS的所有要素,通过定位不同位置的二次铣而形成的所有垂直走线宽度的变化情况。利用这个特点,我们可以创建不同阻抗的垂直走线。图2还显示出二次布线穿过电镀层的方式是不同的,因为在大部分槽周长内,会留下实铜(例如形成厚铜连接)。

图2:VeCS各部分的定义

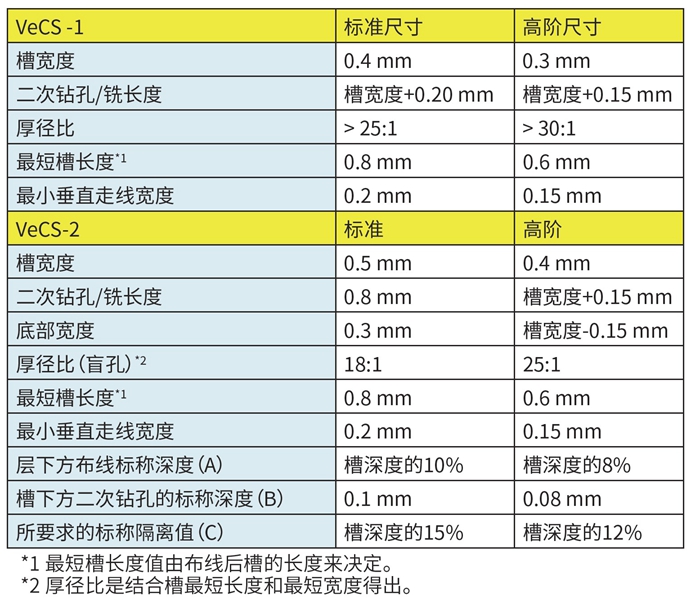

表1所示是我们目前使用的尺寸。虽然我们目前使用的是标准尺寸那一栏的参数,但在不久之后我们就会使用高阶尺寸用参数。在开始设计之前,一定要和PCB制造商核实验证这些数值的可行性。

表1:VeCS-1和VeCS-2的设计准则

焊盘定义

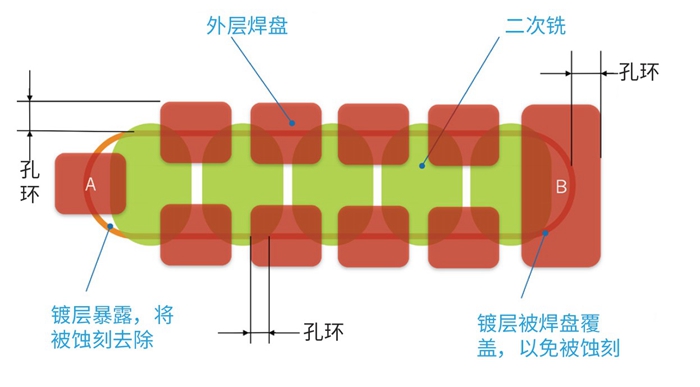

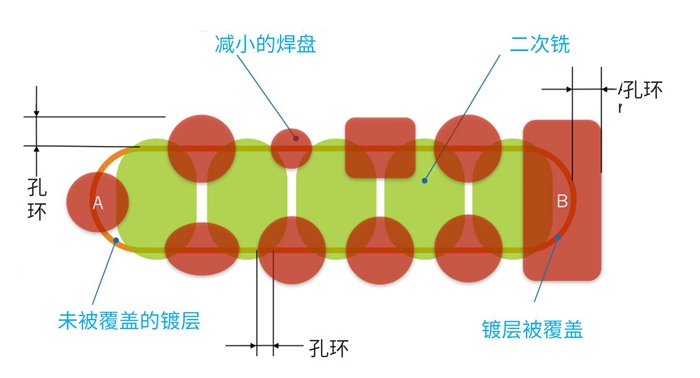

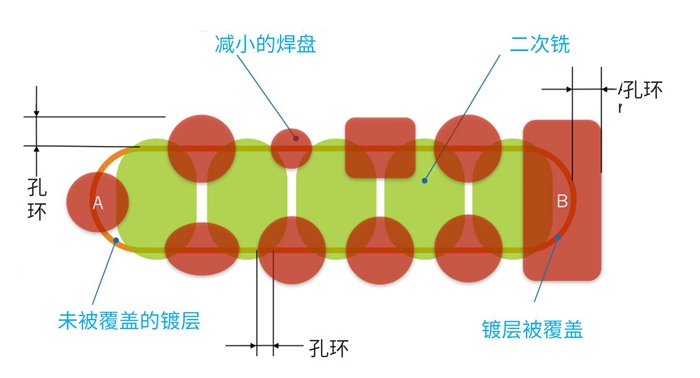

对于外层而言,或者在使用VeCS垂直走线时,一般规则是我们要确认孔有镀层。在确定焊盘尺寸时,我们要考虑到制孔技术可能会导致对准有偏差。在图3中,用圆角正方形和圆角长方形来表示外层焊盘。只要遵循规则,圆形焊盘或任何其他形状的焊盘都可行。

A焊盘有电镀层外露,会被蚀刻去除,产生开路,或是在组装过程或使用过程中出现连接断裂。B焊盘覆盖了电镀层的整个部分,可防止镀层被蚀刻去除。

图3:外层焊盘定义

对于内层,我们有类似的设置(图4),规则要简单很多。我们必须确保考虑到使用焊盘可能会造成的对准误差,以保证内层铜层和电镀层之间的连接。我们还要让焊盘与槽有足够的重叠区域,以弥补对准偏差,并保证焊盘始终会接触镀层。一般情况下,在形成槽时会铣掉一半的焊盘。焊盘尺寸减小的例子说明较小尺寸的焊盘也是可能的,但像钻孔一样,在铣槽时可能会拉出焊盘。

图4:内层焊盘定义

在图4中,我们使用了不同形状及不同尺寸的焊盘。可选择最适合你的焊盘,不使用焊盘也是一种选择。当水平走线与垂直走线的宽度接近时,若二次铣及内层与设计裕度不一致,那么小小的对准误差都有可能造成开路。

内层不会出现蚀刻掉电镀层的问题。焊盘A的情况是有效的,唯一重要的是CAD系统中的DRC功能一定要将电镀层纳入考虑范围,而通常起决定性因素的是焊盘。

孔环的尺寸要求是最小为0.1 mm,以防止孔破出。在按照尺寸/设计规则开始设计之前要咨询PCB制造商。在VeCS设计中也可去除非功能焊盘。

在下面的内容中,我们会讲解Cadence公司如何将VeCS应用到Allegro设计系统中。和第一部分描述的设计准则有所不同的是,对于二次铣我们采用了二次钻孔。在空间允许的前提下可采用二次钻孔。

Cadence Allegro系统中的VeCS结构概述

在Allegro Symbol Editor中用引脚和导通孔等将VeCS结构生成为机械符号。然后将这些机械符号按需放置到设计中进行布线,不需要在原理图上添加VeCS结构符号。标准的VeCS结构可以采用贯通孔的钻孔特征(VeCS-1),也可用盲孔的钻孔特征(VeCS-2)来构建。

下文是VeCS结构中不同实体的具体描述(图5):

· 被定义为引脚的电镀槽

-

没有分配逻辑引脚编号的引脚

· 定义为引脚的非电镀槽分隔符

-

可用于间距更细BGA引脚的槽孔

· 连接导通孔,定义为带有残桩走线的导通孔

-

一旦残桩走线末端接触到了BGA引脚中心,导通孔就会采用BGA引脚网

-

为了加快创建速度,连接导通孔/桩线的排列方式可以在布局中设置好,随后再使用子图形导入Symbol Editor中

· 将不同对象排列成最终的VeCS结构

· 提示:引脚/导通孔采用的焊盘和钻孔尺寸由其设计中的应用所决定(即BGA间距和焊料球焊盘尺寸)。

图5:VeCS结构中的不同实体

焊盘堆叠生成(1mm BGA/0.045mm焊料球焊盘)

电镀槽

· 电镀槽作为那些不直接连接到网的结构基础(图6)

· 钻孔=5.254 mm x 0.254 mm

-

X尺寸槽=BGA焊盘的连接跨度+Y尺寸槽

· 常规焊盘(所有层)/掩膜焊盘(外层)=5.508 mm x 0.508 mm的椭圆形

· 反焊盘=5.127 mm x 0.127 mm的椭圆形

-

反焊盘尺寸要小于钻孔尺寸,这样才能让连接导通孔附着在负片的槽孔壁上

-

连接导通孔上的反焊盘与非电镀孔的禁布区会隔离开不连接的位置

· 散热盘(所有层)=无

-

电镀槽没有直接连接,不需要散热

· 相邻层的禁布区=5.508 mm x 0.508 mm的椭圆形

-

VeCS-2机械钻孔的过冲幅度间隙(盲深度)

· 镀槽的放置位置

-

以正交方向放于BGA焊料球焊盘之间(图7)

图6:电镀槽

由于篇幅有限,更多内容请点击在线或下载查阅。